# TMPR3922U

TENTATIVE

(32 bit RISC Microprocessor)

### 1. GENERAL DESCRIPTION

The TMPR3922U is a single-chip integrated digital ASSP for PDA(Personal Digital Assistants). The TMPR3922U consists of PDA system support logic, integrated with the TX3920 processor Core designed by Toshiba.

### 2. FEATURES

- R3000A-based TX3920 Processor Core

RISC architecture developed by MIPS Technologies, Inc.

Toshiba has added its own multiply-add and branch-likely instructions.

A single-cycle multiply/accumulate module to allow integrated DSP functions, such as a software modem for high-performance standard data and fax protocols

Instruction cache: 16K bytes(2Way); data cache : 8K bytes(2Way)

On-chip Translation Lookaside Buffer (TLB) with  $64 \times 64$ -bit wide entries, each of which maps 4K/16K/64K/256K/1M/4M Byte page

Max 166MHz operation

- Built-in peripheral circuit

- Clock generator with built-in sixteenfold-frequency phase-locked loop (PLL)

Four-stage write buffer

A high performance and flexible Bus Interface Unit

Multiple DMA channels

Memory controller for DRAM(EDO), SDRAM, SRAM, ROM, Flash Memory and PCMCIA

Power management unit

Big / Little endian

- Low power dissipation

3.3V(I/O) / 2.5V(Internal) operation

Standby Current 10mA(typ)

CPU clock stop mode

Power down modes for individual internal peripheral modules

- Plastic LQFP 208-pin package

•The information contained herein is subject to change without notice.

•TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook

• The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

R3000A is a trademark of MIPS Technologies, Inc.

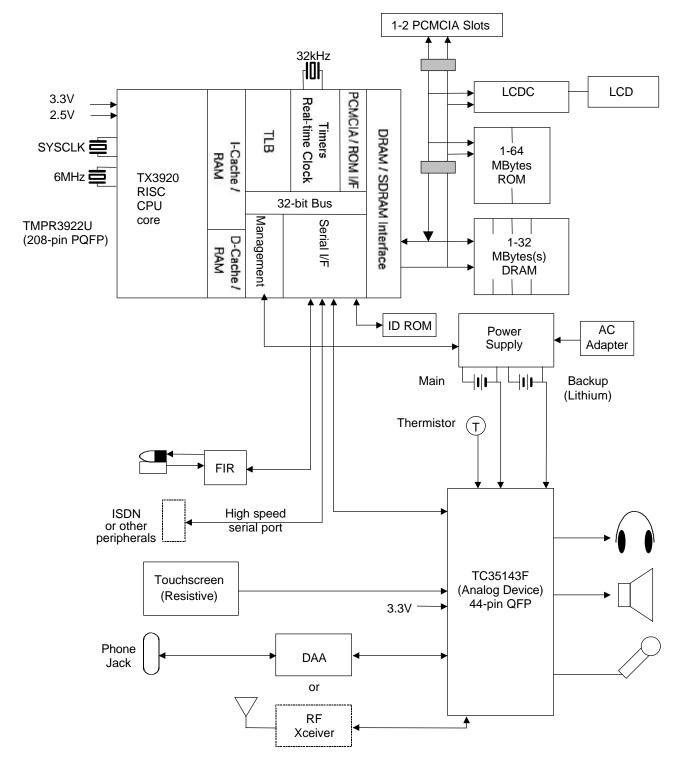

# 3. SYSTEM CONFIGURATION

# 3.1 SYSTEM BLOCK DIAGRAM

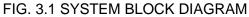

## 3.2 TMPR3922U DIAGRAM

FIG. 3.2 TMPR3922U BLOCK DIAGRAM

# 3.3 MEMORY CONNECTIONS

D [31:0] Data Bus and Cas\* signals change the name of the pins in the Little Endian mode as follows.

| D [31:24]      | becomes            | D[7:0]         |

|----------------|--------------------|----------------|

| D [23:16]      | becomes            | D[15:8]        |

| D [15:8]       | becomes            | D[23:16]       |

| D [7:0]        | becomes            | D[31:24]       |

|                |                    |                |

|                |                    |                |

| CAS3*          | becomes            | CAS0*          |

| CAS3*<br>CAS2* | becomes<br>becomes | CAS0*<br>CAS1* |

|                |                    |                |

<Note>

The connection between the TMPR3922U and Memory depends on the endianess.

# 3.3.1 MEMORY CONNECTIONS (Big Endian)

| TMPR3922U | Pin No.   |                  |                | Bank0 |      |         |

|-----------|-----------|------------------|----------------|-------|------|---------|

| D[31]     | 133 D[31] |                  |                | 16bit |      |         |

| 5         | 5         | CAS1*            | CASHI*         | DRAM  |      |         |

| D[24]     | 145 D[24] | CAS0*            | CASLO*         |       |      |         |

| D[23]     | 146 D[23] |                  |                |       | DATA | D[15:0] |

| ς         | 5         |                  |                |       |      |         |

| D[16]     | 159 D[16] | RAS0*            | RAS*           |       |      |         |

| D[15]     | 27 D[15]  | WE*              | WE*            |       |      |         |

| ς         | 5         | A[12:0]          | ADDR           |       |      |         |

| D[8]      | 16 D[8]   |                  |                |       |      |         |

| D[7]      | 14 D[7]   |                  |                |       |      |         |

| ς         | 5         |                  |                |       |      |         |

| D[0]      | 2 D[0]    |                  |                |       |      |         |

|           |           |                  |                | Bank1 |      |         |

| CAS3*     | 195 CAS3* | CAS3*            | CAS HI*        | 32bit |      |         |

| CAS2*     | 197 CAS2* | CAS2*            | CAS MH*        |       |      |         |

| CAS1*     | 198 CAS1* | CAS1*            | CAS ML*        |       |      |         |

| CAS0*     | 199 CAS0* | CAS0*            | CAS LO*        |       | DATA | D[31:0] |

| RAS0*     | 194 RAS0* | <b>D</b> 4 0 0 t | <b>D</b> 4 0 ± |       |      |         |

|           |           |                  | RAS*           |       |      |         |

| WE*       | 169 WE*   | WE*<br>A[12:0]   | WE*<br>ADDR    |       |      |         |

| A[12:0]   | A[12:0]   |                  |                |       |      |         |

<u>Big Endian</u>

# 3.3.2 MEMORY CONNECTIONS (Little Endian)

| <b>TMPR3922U</b> | Pin No.   |         |         | BANK0 |             |

|------------------|-----------|---------|---------|-------|-------------|

| D[31]            | 14 D[31]  |         |         | 16bit |             |

| ς                | S         | CAS1*   | CASHI*  | DRAM  |             |

| D[24]            | 2 D[24]   | CAS0*   | CASLO*  |       |             |

| D[23]            | 27 D[23]  |         |         |       | DATA D[15:0 |

| ς                | ς         |         |         |       |             |

| D[16]            | 16 D[16]  | RAS0*   | RAS*    |       |             |

| D[15]            | 146 D[15] | WE*     | WE*     |       |             |

| ς                | 5         | A[12:0] | ADDR    |       |             |

| D[8]             | 159 D[8]  |         |         |       |             |

| D[7]             | 133 D[7]  |         |         |       |             |

| ς                | 5         |         |         |       |             |

| D[0]             | 145 D[0]  |         |         |       |             |

|                  |           |         |         | BANK1 |             |

| CAS3*            | 199 CAS3* | CAS3*   | CAS HI* | 32bit |             |

| CAS2*            | 198 CAS2* | CAS2*   | CAS MH* |       |             |

| CAS1*            | 197 CAS1* | CAS1*   | CAS ML* |       |             |

| CAS0*            | 195 CAS0* | CAS0*   | CAS LO* |       | DATA D[31:0 |

| RAS0*            | 194 RAS0* |         |         |       |             |

|                  |           | _RAS0*  | RAS*    |       |             |

| WE*              | 169 WE*   | WE*     | WE*     |       |             |

|                  |           |         |         |       |             |

| A[12:0]          | A[12:0]   | A[12:0] | ADDR    |       |             |

Little Endian

# 4. PINS

#### TENTATIVE **4.1 PIN ASSIGNMENT** NO. I/O SIGNAL NAME NO. I/O SIGNAL NAME NO. I/O SIGNAL NAME 1 VDDH 41 Т SIBDIN 81 VSS \_ \_ 2 I/O 42 Ο SIBDOUT 82 **PWRCS** D[0] (D [24]) 0 3 VSS 43 VDDH Т **PWRINT** \_ \_ 83 4 I/O D[1] (D [25]) 44 SIBIRQ Т **PWROK** Т 84 NC RESERVED I/O IO[8] 5 I/O D[2] (D [26]) 45 85 6 NC Т ONBUTN VDDH 46 RESERVED 86 PON\* 7 I/O D[3] (D [27]) 47 NC RESERVED 87 L 8 VSS 48 VSS 88 Т **CPURES\*** \_ \_ 9 I/O D[4] (D [28]) 49 I/O CHICLK VDDH 89 \_ 10 \_ VDDLS 50 I/O CHIFS 90 Т C6MIN 11 I/O D[5] (D [29]) 51 L CHIDIN 91 Ο C6MOUT 12 0 CHIDOUT I/O D[6] (D [30]) 52 92 \_ VSS I/O 13 VSS 53 VDDH 93 IO[9] \_ \_ 14 I/O D[7] (D [31]) 54 L RXD I/O IO[10] 94 15 IO[11] VSS 55 0 TXD 95 I/O \_ 16 I/O D[8] (D [16]) 56 Т IRINA VSSP(PLL) 96 \_ 17 VDDH **IRINB** VDDP(PLL) \_ 57 Т 97 \_ 18 I/O 0 FIROUT 0 C48MOUT D[9] (D [17]) 58 98 19 I/O D[10] (D [18]) 59 Ο IROUT I/O 99 IO[7] 20 VSS VSS I/O \_ 60 \_ 100 IO[6] 21 I/O D[11] (D [19]) 61 \_ VDDH 101 I/O IO[5] VSSP(PLL) 22 VDDH 62 T CARDET 102 \_ \_ 23 I/O D[12] (D [20]) 63 0 **RXPWR** 103 I/O IO[1] VDDP(PLL) 24 I/O D[13] (D [21]) I/O IO[3] 104 \_ 64 25 VSS 65 I/O IO[2] 105 CARD2WAIT\* \_ Т 26 VSS I/O D[14] (D [22]) 66 \_ 106 0 CARD2CSH\* 27 I/O D[15] (D [23]) 0 SPICLK 107 0 CARD2CSL\* 67 28 SPIIN 108 I/O \_ VDDH 68 Т IO[0] **ENDIAN** VSS 29 Т 69 Ο SPIOUT 109 \_ 30 JTDI VDDLS CARDIORD\* Т 70 110 0 \_ 31 0 JTDO 71 Т TESTCPU 111 0 CARDIOWR\* 32 Т JTMS 72 Т TESTIN 112 0 CARDREG\* 33 \_ VSS 73 0 BCLK 113 Т CARD1WAIT\* 34 JTCK 74 Т **TESTAIU** 114 VDDH Т \_ NC RESERVED VSS CARDDIR\* 35 75 115 \_ Ο VDDLS 36 VDDLS 76 L VCC3 116 \_ \_ 37 0 SIBMCLK 77 Ο BC32K 117 CARD1CSL\* 0 38 VSS VDDH 0 CARD1CSH\* \_ 78 \_ 118 39 0 SIBSCLK 79 C32KIN VSS Т 119 \_ 40 Ο SIBSYNC 80 Ο C32KOUT 120 MCS1WAIT\* L

\*Active-low signal

() indicates the signal name in the Little endian mode

| TENTATIVE |  |

|-----------|--|

|           |  |

| NO.    | I/O     | SIGNAL NAME    | NO. | I/O | SIGNAL NAME          | NO.    | I/O      | SIGNAL NAME        |

|--------|---------|----------------|-----|-----|----------------------|--------|----------|--------------------|

| 121    | Ι       | MCS0WAIT*      | 161 | I/O | IO[4]                | 201    | _        | VDDL               |

| 122    | 0       | MCS1*          | 162 | 0   | CS0*                 | 202    | 0        | DCKE               |

| 123    | 0       | MCS0*          | 163 | 0   | RD*                  | 203    | I        | VSS                |

| 124    | 0       | CS3*           | 164 | _   | VSS                  | 204    | -        | DCLKIN             |

| 125    | 0       | CS2*           | 165 | _   | VDDLS                | 205    | 0        | DCLKOUT            |

| 126    | 0       | CS1*           | 166 | 0   | DGRNT*               | 206    | -        | VDDH               |

| 127    | -       | VDDH           | 167 | I   | DREQ*                | 207    | 0        | DQMH               |

| 128    | I       | SYSCLKIN       | 168 | 0   | ALE                  | 208    | 0        | DQML               |

| 129    | 0       | SYSCLKOUT      | 169 | 0   | WE*                  |        |          |                    |

| 130    | _       | VSS            | 170 | _   | VDDH                 |        |          |                    |

| 131    | _       | VSS            | 171 | I/O | A[12]                |        |          |                    |

| 132    | _       | VDDLS          | 172 | I/O | A[11]                |        |          |                    |

| 133    | I/O     | D[31] (D [7])  | 173 | _   | VSS                  |        |          |                    |

| 134    | I/O     | D[30] (D [6])  | 174 | I/O | A[10]                |        |          |                    |

| 135    | _       | VSS            | 175 | I/O | A[9]                 |        |          |                    |

| 136    | I/O     | D[29] (D [5])  | 176 | _   | VDDL                 |        |          |                    |

| 137    | _       | VDDH           | 177 | I/O | A[8]                 |        |          |                    |

| 138    | I/O     | D[28] (D [4])  | 178 | I/O | A[7]                 |        |          |                    |

| 139    | I/O     | D[27] (D [3])  | 179 | _   | VSS                  |        |          |                    |

| 140    | _       | VSS            | 180 | I/O | A[6]                 |        |          |                    |

| 141    | I/O     | D[26] (D [2])  | 181 | I/O | A[5]                 |        |          |                    |

| 142    | _       | VSS            | 182 | _   | VDDH                 |        |          |                    |

| 143    | I/O     | D[25] (D [1])  | 183 | I/O | A[4]                 |        |          |                    |

| 144    | _       | VDDLS          | 184 | _   | VSS                  |        |          |                    |

| 145    | I/O     | D[24] (D [0])  | 185 | I/O | A[3]                 |        |          |                    |

| 146    | I/O     | D[23] (D [15]) | 186 | I/O | A[2]                 |        |          |                    |

| 147    | _       | VDDH           | 187 | _   | VDDL                 |        |          |                    |

| 148    | I/O     | D[22] (D [14]) | 188 | I/O | A[1]                 |        |          |                    |

| 149    | -       | VSS            | 189 | I/O | A[0]                 |        |          |                    |

| 150    | I/O     | D[21] (D [13]) | 190 | _   | VSS                  |        |          |                    |

| 151    | -       | VDDH           | 191 | _   | VSS                  |        |          |                    |

| 152    | I/O     | D[20] (D [12]) | 192 | 0   | DCS0*                |        |          |                    |

| 153    | I/O     | D[19] (D [11]) | 193 | 0   | RAS1*                |        |          |                    |

| 154    | _       | VSS            | 194 | 0   | RAS0*                |        |          |                    |

| 155    | I/O     | D[18] (D [10]) | 195 | 0   | CAS3* (CAS0*)        |        |          |                    |

| 156    | _       | VDDLS          | 196 | _   | VDDH                 |        |          |                    |

| 157    | I/O     | D[17] (D [9])  | 197 | 0   | CAS2* (CAS1*)        |        |          |                    |

| 158    | _       | VSS            | 198 | 0   | CAS1* (CAS2*)        |        |          |                    |

| 159    | I/O     | D[16] (D [8])  | 199 | 0   | CAS0* (CAS3*)        |        |          |                    |

| 160    | _       | VDDH           | 200 | _   | VSS                  |        |          |                    |

| *Activ | e-low s | ignal          |     |     | () indicates the sig | nalnam | a in tha | Little endian mode |

\*Active-low signal

() indicates the signal name in the Little endian mode

# 4.2 PIN FUNCTIONS

# Memory Pins

| NAME         | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[31:0]      | I/O | These pins are the data bus for the system. 16-bit SDRAMs and DRAMs should be connected to bits 15:0. All other 16-bit ports should be connected to bits 31:16. Of course, 32-bit ports should be connected to be bits 31:0. These pins are normally outputs and only become inputs during reads, thus no resistors are required since the bus will only float for a short period of time during bus turn-around.                                                                                                 |

| A[12:0]      | 0   | These pins are the address bus for the system. The address lines are multiplexed and can be connected directly to SDRAM and DRAM devices. To generate the full 26-bit address for static devices, an external latch must be used to latch the signals using the ALE signal. For static devices, address bits 25:13 are provided by the external latch and address bits 12:0 (directly connected from the TMPR3922U's address bus) are held afterward by the TMPR3922U for the remainder of the address bus cycle. |

| ALE          | 0   | This pin is used as the address latch enable to latch A[12:0] using an external latch, for generating the upper address bits 25:13.                                                                                                                                                                                                                                                                                                                                                                               |

| RD*          | 0   | This pin is used as the read signal for static devices. This signal is asserted for reads from MC3*-0*, CS3*-0*, CARD2CS* and CARD1CS* for memory and attribute space, and for reads from the TMPR3922U accesses if SHOWDINO is enabled (for debugging purposes).                                                                                                                                                                                                                                                 |

| WE*          | 0   | This pin is used as the write signal for system. This signal is asserted for writes to MC3*-0*, CS3*-0*, CARD2CS* and CARD1CS* for memory and attribute space, and for writes to DRAM and SDRAM.                                                                                                                                                                                                                                                                                                                  |

| CAS0*(WE0*)  | 0   | This pin is used as the CAS signal for SDRAMs, the CAS signal for D[7:0] for DRAMs, and the write enable signal for D[7:0] for static devices.                                                                                                                                                                                                                                                                                                                                                                    |

| CAS1*(WE1*)  | 0   | This pin is used as the CAS signal for D[15:8] for DRAMs, and the write enable signal for D[15:8] for static devices.                                                                                                                                                                                                                                                                                                                                                                                             |

| CAS2*(WE2*)  | 0   | This pin is used as the CAS signal for D[23:16] for DRAMs, and the write enable signal for D[23:16] for static devices.                                                                                                                                                                                                                                                                                                                                                                                           |

| CAS3*(WE3*)  | 0   | This pin is used as the CAS signal for D[31:24] for DRAMs, and the write enable signal for D[31:24] for static devices.                                                                                                                                                                                                                                                                                                                                                                                           |

| RAS0*        | 0   | This pin is used as the RAS signal for SDRAMs and the RAS signal for Bank0 DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RAS1*(DCS1*) | 0   | This pin is used as the chip select signal for Bank1 SDRAMs and the RAS signal for Bank1 DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                   |

\*Active-low signal

| NAME          | I/O | DESCRIPTION                                                                       |

|---------------|-----|-----------------------------------------------------------------------------------|

| DCS0*         | 0   | This pin is used as the chip select signal for Bank0 SDRAMs.                      |

| DCKE          | 0   | This pin is used as the clock enable for SDRAMs.                                  |

| DCLKIN        | Ι   | This pin must be tied externally to the DCLKOUT signal and is used to match       |

|               |     | skew for the data input when reading from SDRAM and DRAM devices.                 |

| DCLKOUT       | 0   | This pin is the (nominal) 82.944MHz clock for the SDRAMs.                         |

| DQMH          | 0   | This pin is the upper data mask for a 16-bit SDRAM configuration.                 |

| DQML          | 0   | This pin is the lower data mask for a 16-bit SDRAM or an 8-bit SDRAM              |

|               |     | configuration.                                                                    |

| CS3-0*        | 0   | These pins are the Chip Select 3 through 0 signals. They can be configured to     |

|               |     | support either 32-bit or 16-bit ports.                                            |

| MCS1-0*       | 0   | These pins are the Chip Select 1 through 0 signals for the external device.       |

|               |     | They can be configured to support either 32-bit or 16-bit ports.                  |

| CARD2CSH*, L* | 0   | These pins are the Chip Select signals for PCMCIA card slot 2.                    |

| CARD1CSH*, L* | 0   | These pins are the Chip Select signals for PCMCIA card slot 1.                    |

| CARDREG*      | 0   | This pin is the REG* signal for the PCMCIA cards.                                 |

| CARDIORD*     | 0   | This pin is the IORD* signal for the PCMCIA IO cards.                             |

| CARDIOWR*     | 0   | This pin is the IOWR* signal for the PCMCIA IO cards.                             |

| CARDDIR*      | 0   | This pin is used to provide the direction control for bi-directional data buffers |

|               |     | used for the PCMCIA slot(s). This signal will assert whenever CARD2CSH* or        |

|               |     | CARD2CSL* or CARD1CSH* or CARD1CSL* is asserted and a read                        |

|               |     | transaction is taking place.                                                      |

| CARD2WAIT*    | Ι   | This pin is the card wait signal from PCMCIA card slot 2.                         |

| CARD1WAIT*    | I   | This pin is the card wait signal from PCMCIA card slot 1.                         |

| MCS1WAIT*     | I   | This pin is the wait signal from the external device 1.                           |

| MCS0WAIT*     | Ι   | This pin is the wait signal from the external device 0.                           |

\*Active-low signal

• Bus Arbitration Pins

| NAME   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DREQ*  | I   | This pin is used to request external arbitration. If the TESTAIU signal is high<br>and the TESTAIU function has been enabled, then once DGRNT* is asserted,<br>external logic can initiate reads or writes to the TMPR3922U registers by<br>driving the appropriate input signals. If the TESTAIU signal is low or the<br>TESTAIU function has not been enabled, then the TMPR3922U memory<br>transactions are halted and certain memory signals will be tri-stated when<br>DGRNT* is asserted in order to allow an external master to access memory. |

| DGRNT* | 0   | This pin is asserted in response to DREQ* to inform the external test logic or bus master that it can now begin to drive signals.                                                                                                                                                                                                                                                                                                                                                                                                                     |

\*Active-low signal

# · Clock Pins

| NAME      | I/O | DESCRIPTION                                                              |

|-----------|-----|--------------------------------------------------------------------------|

| SYSCLKIN  | Ι   | This pin should be connected along with SYSCLKOUT to an external crystal |

|           |     | which is the main TMPR3922U clock source.                                |

| SYSCLKOUT | 0   | This pin should be connected along with SYSCLKIN to an external crystal  |

|           |     | which is the main TMPR3922U clock source.                                |

| C32KIN    | Ι   | This pin along with C32KOUT should be connected to a 32.768 kHz crystal. |

| C32KOUT   | 0   | This pin along with C32KIN should be connected to a 32.768 kHz crystal.  |

| C6MIN     | I   | This pin along with C6MOUT should be connected to a 6 MHz crystal.       |

| C6MOUT    | 0   | This pin along with C6MIN should be connected to a 6 MHz crystal.        |

| C48MOUT   | 0   | This pin is a buffered output of the 48 MHz clock.                       |

| BC32K     | 0   | This pin is a buffered output of the 32.768 kHz clock.                   |

| BCLK      | 0   | This pin is a reference clock for the external device.                   |

#### CHI Pins

| NAME    | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                            |

|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHIFS   | I/O | This pin is the CHI frame synchronization signal. This pin is available for use in one of two modes. As an output, this pin allows the TMPR3922U to be the master CHI sync source. As an input, this pin allows an external peripheral to be the master CHI sync source and the TMPR3922U CHI module will slave to this external sync. |

| CHICLK  | I/O | This pin is the CHI clock signal. This pin is available for use in one of two modes. As an output, this pin allows the TMPR3922U to be the master CHI clock source. As an input, this pin allows an external peripheral to be the master CHI clock source and the TMPR3922U CHI module will slave to this external clock.              |

| CHIDOUT | 0   | This pin is the CHI serial data output signal.                                                                                                                                                                                                                                                                                         |

| CHIDIN  | Ι   | This pin is the CHI serial data inaut signal.                                                                                                                                                                                                                                                                                          |

#### • IO Pins

| NAME     | I/O | DESCRIPTION                                                                   |

|----------|-----|-------------------------------------------------------------------------------|

| IO[11:0] | I/O | These pins are general purpose input/output ports. Each port can be           |

|          |     | independently programmed as an input or output port. Each port can generate a |

|          |     | separate positive and negative edge interrupt. Each port can also be          |

|          |     | independently programmed to use a 16 to 24ms debouncer.                       |

# Reset Pins

| NAME         | I/O  | DESCRIPTION                                                                                                                                                                                                                                               |

|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPURES*      | I    | This pin is used to reset the CPU core. This pin should be connected to a switch for initiating a reset in the event that a software problem might hang the CPU core. The pin should also be pulled up to VSTANDBY† through an external pull-up resistor. |

| PON*         | I    | This pin serves as the Power On Reset signal for the TMPR3922U. This signal must remain low when VSTANDBY is asserted until VSTANDBY is stable. Once VSTANDBY† is asserted, this signal should never go low unless all power is lost in the system.       |

| † VSTANDBY : | This | s signal provides power for the TMPR3922U and other components in the system                                                                                                                                                                              |

VSTANDBY : This signal provides power for the TMPR3922U and other components in the system that must never lose power. This signal should always be asserted if there is either a good Main Backup Battery, or if a Battery Charger is plugged in. · Power Supply Pins

| NAME         | I/O | DESCRIPTION                                                                         |

|--------------|-----|-------------------------------------------------------------------------------------|

| ONBUTN       |     | This pin is used as the On Button for the system. Asserting this signal will        |

|              |     | cause PWRCS to set to indicate to the System Power Supply to turn power on          |

|              |     | to the system. PWRCS will not assert if the PWROK signal is low.                    |

| PWRCS        | 0   | This pin is used as the chip select for the System Power Supply. When the           |

|              |     | system is off, the assertion of this signal will cause the System Power Supply      |

|              |     | to turn VCCDRAM <sup>††</sup> and VCC3 on to power up the system. The Power Supply  |

|              |     | will latch SPI commands on the falling edge of PWRCS.                               |

| PWROK        | Ι   | This pin provides a status from the System Power Supply that there is a good        |

|              |     | source of power in the system. This signal typically will be asserted if there is a |

|              |     | Battery Charger supplying current or if the Main Battery is good and the Battery    |

|              |     | Door is closed. If PWROK is low when the system is powered off, PWRCS will          |

|              |     | not assert as a result of the user pressing the ONBUTN or an interrupt              |

|              |     | attempting to wake up the system. If the device is on when the PWROK signal         |

|              |     | goes low, the software will immediately shut down the system since power is         |

|              |     | about to be lost. When PWROK goes low, there must be ample warning so that          |

|              |     | the software can shut down the system before power is actually lost.                |

| PWRINT       | I   | This pin is used by the System Power Supply to alert the software that some         |

|              |     | status has changed in the System Power Supply and the software should read          |

|              |     | the status from the System Power Supply to find out what has changed. These         |

|              |     | will be low priority events, unlike the PWROK status, which is a high priority      |

|              |     | emergency case.                                                                     |

| VCC3         | I   | This pin provides the status of the power supply for the ROM, BETTY, system         |

|              |     | buffers, and other transient components in the system. This signal will be          |

|              |     | asserted by the System Power Supply when PWRCS is asserted, and will                |

|              |     | always be turned off when the system is powered down.                               |

| †† VCCDRAM : | TI  | his signal provides power for the DRAM and/or SDRAM. This supply must be off        |

CDRAM : This signal provides power for the DRAM and/or SDRAM. This supply must be off when VSTANDBY is first asserted, and remain off until the system is powered up by the assertion of PWRCS. When the software subsequently powers down the system it may choose to keep this supply on to preserve the contents of memory.

# SIB Pins

| NAME    | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SIBDIN  | I   | This pin contains the input data shifted from BETTY and/or external codec device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SIBDOUT | 0   | This pin contains the output data shifted to BETTY and/or external codec device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SIBSCLK | 0   | This pin is the serial clock sent to BETTY and/or external codec device. The programmable SIBSCLK rate is derived by dividing down from SIBMCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SIBSYNC | 0   | This pin is the frame synchronization signal sent to BETTY and/or external codec device. This frame sync is asserted for one clock cycle immediately before each frame starts and all devices connected to the SIB monitor SIBSYNC to determine when they should transmit or receive data.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| SIBIRQ  | I   | This pin is a general purpose input port used for the SIB interrupt source from BETTY. This interrupt source can be configured to generate an interrupt on either a positive and/or negative edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| SIBMCLK | I/O | This pin is the master clock source for the SIB logic. This pin is available for use in one of two modes. First, SIBMCLK can be configured as a high-rate output master clock source required by certain external codec devices. In this mode all SIB clocks are synchronously slaved to the main TMPR3922U system clock CLK2X. Conversely, SIBMCLK can be configured as an input slave clock source. In this mode, all SIB clocks are derived from an external SIBMCLK oscillator source, which is asynchronous with respect to CLK2X. Also, for this mode, SIBMCLK can still be optionally used as a high-rate master clock source required by certain external codec devices. |  |  |  |  |

#### SPI Pins

| NAME   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPICLK | I/O | This pin is used to clock data in and out of either the SPI master or slave device. This pin is the master clock source for the SPI logic. This pin is available for use in one of two modes. First, SPICLK can be configured as a master clock source required by certain external devices. In this mode all SPI clocks are synchronously slaved to the main TMPR3922U system clock FREECLK. Conversely, SPICLK can be configured as an input slave clock source. In this mode, all SPI clocks are derived from an external oscillator source, which is asynchronous with respect to FREECLK. |

| SPIOUT | 0   | This pin contains the data that is shifted into the SPI slave device .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SPIIN  | Ι   | This pin contains the data that is shifted out of the SPI slave device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

# · UART and SIR/FIR Pins

| NAME   | I/O | DESCRIPTION                                                                      |  |  |  |

|--------|-----|----------------------------------------------------------------------------------|--|--|--|

| TXD    | 0   | This pin is the UART transmit signal from the UARTA module.                      |  |  |  |

| RXD    | I   | This pin is the UART receive signal to the UARTA module.                         |  |  |  |

| IROUT  | 0   | This pin is the UART transmit signal from the UARTB module or the Consumer       |  |  |  |

|        |     | IR output signal if Consumer IR mode is enabled.                                 |  |  |  |

| IRINA  | Ι   | This pin is the SIR receive signal to the IRDA(FIR/SIR) module.                  |  |  |  |

| IRINB  | I   | This pin is the FIR receive signal to the IRDA(FIR/SIR) module.                  |  |  |  |

| RXPWR  | 0   | This pin is the receiver power output control signal to the external             |  |  |  |

|        |     | communication IR analog circuitry.                                               |  |  |  |

| CARDET | I   | This pin is the UART receive signal to the UARTB module or is the carrier detect |  |  |  |

|        |     | input signal from the external communication IR analog circuitry if Consumer IR  |  |  |  |

|        |     | module is enabled.                                                               |  |  |  |

| FIROUT | 0   | This pin is the FIR/SIR transmit signal from the IRDA(FIR/SIR) module.           |  |  |  |

## JTAG Pins

| NAME | I/O | DESCRIPTION                                                                                               |  |  |  |

|------|-----|-----------------------------------------------------------------------------------------------------------|--|--|--|

| JTDI | -   | Data is serially scanned in through this pin.                                                             |  |  |  |

| JTDO | 0   | Data is serially scanned out through this pin.                                                            |  |  |  |

| JTMS | Ι   | AG command signal, indicating the incoming serial data is command data                                    |  |  |  |

| JTCK | Ι   | The processor outputs a serial clock on JTCK. On the rising edge of JTCK, both JTDI and JTMS are sampled. |  |  |  |

· Endianess Pins

| NAME   | I/O | DESCRIPTION                                                                           |  |  |  |  |

|--------|-----|---------------------------------------------------------------------------------------|--|--|--|--|

| ENDIAN | Ι   | nis pin is used to select the endianess of the TMPR3922U. The "1" level input         |  |  |  |  |

|        |     | sets the endianess to the big endian, while the "0" level input to the little endian. |  |  |  |  |

#### Test Pins

| NAME    | I/O | DESCRIPTION                                                                                                                                                                                                      |

|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TESTAIU | Ι   | This pin is used to define if the Boot ROM is 16 or 32 bits wide. If the TESTAIU pin is asserted during reset, the BIU will assume a 32-bit Boot ROM. The TESTAIU pin should remain static (either high or low). |

| TESTCPU | I   | This pin is used for debugging purposes only. Then the TESTCPU should not be asserted.                                                                                                                           |

| TESTIN  | Ι   | This pin is used for debugging purposes only. Then the TESTIN should not be asserted.                                                                                                                            |

### • Spare Pins

| NAME     | I/O | DESCRIPTION                                                            |

|----------|-----|------------------------------------------------------------------------|

| RESERVED | NC  | These pins are reserved for future use and should be left unconnected. |

# Power Supply Pins

| NAME      | I/O | DESCRIPTION                                                               |  |  |  |  |

|-----------|-----|---------------------------------------------------------------------------|--|--|--|--|

| VDDH      | V   | These pins are the power pins for the TMPR3922U.(+3.3V)                   |  |  |  |  |

| VDDL      | V   | These pins are the power pins for the TMPR3922U.(+2.5V)                   |  |  |  |  |

| VDDLS     | V   | These pins are the power pins for the TMPR3922U.(+2.5V) In the suspend    |  |  |  |  |

|           |     | mode these pins should be 0V.                                             |  |  |  |  |

| VSS       | G   | These pins are the ground pins for the TMPR3922U.                         |  |  |  |  |

| VDDP      | V   | This pin is the analog power pin for the TMPR3922U. Keep away from other  |  |  |  |  |

| (for PLL) |     | VDD.                                                                      |  |  |  |  |

| VSSP      | G   | This pin is the analog ground pin for the TMPR3922U. Keep away from other |  |  |  |  |

| (for PLL) |     | VSS.                                                                      |  |  |  |  |

#### 4.3 PIN USAGE INFORMATION

This section contains tables summarizing various aspects of the pin usage for the TMPR3922U. TABLE 4.3a lists the standard versus multi-function usage for each TMPR3922U pin, if applicable. Those signal names shown in parentheses are test signals for debugging purposes only. The column showing the multi-function select signal and reset state indicates the internal control signal used to select the multi-function mode, as well as the default configuration of each multi-function pin during reset. The "Bus Arb State" column shows which pins are tri-stated whenever the DGRNT\* signal is asserted in response to a DREQ\*(external bus arbitration request).

TABLE 4.3a TMPR3922U STANDARD and MULTI-FUNCTION PIN USAGE

| TMPR3922U pin | Standard Function<br>(I = input, O = output) | Multi-function | Multi-function select<br>(Reset State:<br>1 = multi-function<br>mode selected;<br>0 = standard function<br>& mode selected) | Bus<br>Arb<br>State |

|---------------|----------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------|

| D[31:0]       | D[31:0] (I/O)                                |                |                                                                                                                             | Hi-Z                |

| A[12:0]       | A[12:0] (I/O)                                |                |                                                                                                                             |                     |

| ALE           | ALE (O)                                      |                |                                                                                                                             | Hi-Z                |

| RD*           | RD* (O)                                      |                |                                                                                                                             | Hi-Z                |

| WE*           | WE* (O)                                      |                |                                                                                                                             | Hi-Z                |

| CAS0* (WE0*)  | CAS0* (O)                                    |                |                                                                                                                             | Hi-Z                |

| CAS1* (WE1*)  | CAS1* (O)                                    |                |                                                                                                                             | Hi-Z                |

| CAS2* (WE2*)  | CAS2* (O)                                    |                |                                                                                                                             | Hi-Z                |

| CAS3* (WE3*)  | CAS3* (O)                                    |                |                                                                                                                             | Hi-Z                |

| RAS0*         | RAS0* (O)                                    |                |                                                                                                                             | Hi-Z                |

| RAS1* (DCS1*) | RAS1* (O)                                    |                |                                                                                                                             | Hi-Z                |

| DCS0*         | DCS0* (O)                                    |                |                                                                                                                             | Hi-Z                |

| DCKE          | DCKE (O)                                     |                |                                                                                                                             | Hi-Z                |

| DCLKIN        | DCLKIN (I)                                   |                |                                                                                                                             |                     |

| DCLKOUT       | DCLKOUT (O)                                  |                |                                                                                                                             | Hi-Z                |

| DQMH          | DQMH (O)                                     |                |                                                                                                                             | Hi-Z                |

| DQML          | DQML (O)                                     |                |                                                                                                                             | Hi-Z                |

| DREQ*         | DREQ* (I)                                    | MIO[27]        | MIOSEL[27] (0)                                                                                                              |                     |

| DGRNT*        | DGRNT* (O)                                   | MIO[26]        | MIOSEL[26] (0)                                                                                                              |                     |

| SYSCLKIN      | SYSCLKIN (I)                                 |                |                                                                                                                             |                     |

| SYSCLKOUT     | SYSCLKOUT (O)                                |                |                                                                                                                             |                     |

| C32KIN        | C32KIN (I)                                   |                |                                                                                                                             |                     |

| C32KOUT       | C32KOUT (O)                                  |                |                                                                                                                             |                     |

| C6MIN         | C6MIN (I)                                    |                |                                                                                                                             |                     |

| C6MOUT        | C6MOUT (O)                                   |                |                                                                                                                             |                     |

| C48MOUT       | C48MOUT (O)                                  |                |                                                                                                                             |                     |

| BC32K         | BC32K(O)                                     | MIO[25]        | MIOSEL[25] (1)                                                                                                              |                     |

| BCLK          | BCLK (O)                                     |                | ,                                                                                                                           |                     |

| JTDI          | JTDI (I)                                     |                |                                                                                                                             |                     |

| JTDO          | JTDO (O)                                     |                |                                                                                                                             |                     |

| JTMS          | JTMS (I)                                     |                |                                                                                                                             |                     |

| JTCK          | JTCK (I)                                     |                |                                                                                                                             |                     |

| TMPR3922U pin | Standard Function<br>(I = input, O = output) | Multi-function | Multi-function select<br>(reset state:<br>1 = Multi-function<br>Mode selected;<br>0 = Standard function<br>& mode selected) | Bus<br>Arb<br>State |

|---------------|----------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------|

| PWRCS         | PWRCS (O)                                    |                |                                                                                                                             |                     |

| PWRINT        | PWRINT (I)                                   |                |                                                                                                                             |                     |

| PWROK         | PWROK (I)                                    |                |                                                                                                                             |                     |

| ONBUTN        | ONBUTN (I)                                   |                |                                                                                                                             |                     |

| CPURES*       | CPURES* (I)                                  |                |                                                                                                                             |                     |

| PON*          | PON* (I)                                     |                |                                                                                                                             |                     |

| TXD           | TXD (O)                                      | MIO[24]        | MIOSEL[24] (0)                                                                                                              |                     |

| RXD           | RXD (I)                                      | MIO[23]        | MIOSEL[23] (0)                                                                                                              |                     |

| CS0*          | CS0* (O)                                     |                |                                                                                                                             | Hi-Z                |

| CS1*          | CS1* (O)                                     | MIO[22]        | MIOSEL[22] (0)                                                                                                              |                     |

| CS2*          | CS2* (O)                                     | MIO[21]        | MIOSEL[21] (0)                                                                                                              |                     |

| CS3*          | CS3* (O)                                     | MIO[20]        | MIOSEL[20] (0)                                                                                                              |                     |

| MCS0*         | MCS0* (O)                                    | MIO[19]        | MIOSEL[19] (1)                                                                                                              |                     |

| MCS1*         | MCS1* (O)                                    | MIO[18]        | MIOSEL[18] (1)                                                                                                              |                     |

| MCS0WAIT*     | MCS0WAIT* (I)                                | MIO[0]         | MIOSEL[0] (1)                                                                                                               |                     |

| MCS1WAIT*     | MCS1WAIT* (I)                                | MIO[1]         | MIOSEL[1] (1)                                                                                                               |                     |

| CHIFS         | CHIFS (I/O)                                  | MIO[31]        | MIOSEL[31] (1)                                                                                                              |                     |

| CHICLK        | CHICLK (I/O)                                 | MIO[30]        | MIOSEL[30] (1)                                                                                                              |                     |

| CHIDOUT       | CHIDOUT (O)                                  | MIO[29]        | MIOSEL[29] (1)                                                                                                              |                     |

| CHIDIN        | CHIDIN (I)                                   | MIO[28]        | MIOSEL[28] (1)                                                                                                              |                     |

| VCC3          | VCC3 (I)                                     |                |                                                                                                                             |                     |

| IO11          | IO11 (I/O)                                   |                |                                                                                                                             |                     |

| IO10          | IO10 (I/O)                                   |                |                                                                                                                             |                     |

| IO9           | IO9 (I/O)                                    |                |                                                                                                                             |                     |

| IO8           | IO8 (I/O)                                    |                |                                                                                                                             |                     |

| 107           | IO7 (I/O)                                    |                |                                                                                                                             |                     |

| IO6           | IO6 (I/O)                                    |                |                                                                                                                             |                     |

| IO5           | IO5 (I/O)                                    |                |                                                                                                                             |                     |

| IO4           | IO4 (I/O)                                    |                |                                                                                                                             |                     |

| IO3           | IO3 (I/O)                                    |                |                                                                                                                             |                     |

| IO2           | IO2 (I/O)                                    |                |                                                                                                                             |                     |

| IO1           | IO1 (I/O)                                    |                |                                                                                                                             |                     |

| IO0           | IO0 (I/O)                                    |                |                                                                                                                             |                     |

| SPICLK        | SPICLK (I/O)                                 | MIO[15]        | MIOSEL[15] (0)                                                                                                              |                     |

| SPIOUT        | SPIOUT (O)                                   | MIO[14]        | MIOSEL[14] (0)                                                                                                              |                     |

| SPIIN         | SPIIN (I)                                    | MIO[13]        | MIOSEL[13] (0)                                                                                                              |                     |

| TMPR3922U pin | standard function<br>(I = input, O = output) | multi-function | <ul> <li>multi-function select<br/>(reset state:</li> <li>1 = multi-functzon<br/>mode selected;</li> <li>0 = standard function<br/>&amp; mode selected)</li> </ul> | Bus<br>Arb<br>State |

|---------------|----------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| SIBSYNC       | SIBSYNC (O)                                  |                |                                                                                                                                                                    |                     |

| SIBDOUT       | SIBDOUT (O)                                  |                |                                                                                                                                                                    |                     |

| SIBDIN        | SIBDIN (I)                                   |                |                                                                                                                                                                    |                     |

| SIBMCLK       | SIBMCLK (I/O)                                | MIO[12]        | MIOSEL[12] (0)                                                                                                                                                     |                     |

| SIBSCLK       | SIBSCLK (O)                                  |                |                                                                                                                                                                    |                     |

| SIBIRQ        | SIBIRQ (I)                                   |                |                                                                                                                                                                    |                     |

| RXPWR         | RXPWR (O)                                    | MIO[17]        | MIOSEL[17] (1)                                                                                                                                                     |                     |

| CARDET        | CARDET (I)                                   | MIO[16]        | MIOSEL[16] (1)                                                                                                                                                     |                     |

| IROUT         | IROUT (O)                                    |                |                                                                                                                                                                    |                     |

| IRINA         | IRINA (I)                                    |                |                                                                                                                                                                    |                     |

| IRINB         | IRINB (I)                                    |                |                                                                                                                                                                    |                     |

| FIROUT        | FIROUT (O)                                   |                |                                                                                                                                                                    |                     |

| TESTAIU       | TESTAIU (I)                                  |                |                                                                                                                                                                    |                     |

| TESTCPU       | TESTCPU (I)                                  |                |                                                                                                                                                                    |                     |

| TESTIN        | TESTIN (I)                                   |                |                                                                                                                                                                    |                     |

| CARDREG*      | CARDREG*(O)                                  | MIO[11]        | MIOSEL[11] (1)                                                                                                                                                     |                     |

| CARDIOWR*     | CARDIOWR* (O)                                | MIO[10]        | MIOSEL[10] (1)                                                                                                                                                     |                     |

| CARDIORD*     | CARDIORD* (O)                                | MIO[9]         | MIOSEL[9] (1)                                                                                                                                                      |                     |

| CARD1CSL*     | CARD1CSL* (O)                                | MIO[8]         | MIOSEL[8] (1)                                                                                                                                                      |                     |

| CARD1SCH*     | CARD1CSH* (O)                                | MIO[7]         | MIOSEL[7] (1)                                                                                                                                                      |                     |

| CARD2CSL*     | CARD2CSL* (O)                                | MIO[6]         | MIOSEL[6] (1)                                                                                                                                                      |                     |

| CARD2CSH*     | CARD2CSH* (O)                                | MIO[5]         | MIOSEL[5] (1)                                                                                                                                                      |                     |

| CARD1WAIT*    | CARD1WAIT* (I)                               | MIO[4]         | MIOSEL[4] (1)                                                                                                                                                      |                     |

| CARD2WAIT*    | CARD2WAIT* (I)                               | MIO[3]         | MIOSEL[3] (1)                                                                                                                                                      |                     |

| CARDDIR*      | CARDDIR* (O)                                 | MIO[2]         | MIOSEL[2] (1)                                                                                                                                                      |                     |

| ENDIAN        | ENDIAN (I)                                   |                |                                                                                                                                                                    |                     |

| VDDH          | +3.3V                                        |                |                                                                                                                                                                    |                     |

| VDDL          | +2.5V                                        |                |                                                                                                                                                                    |                     |

| VDDLS         | + 2.5 V / GND                                |                |                                                                                                                                                                    |                     |

| VDDP          | +2.5V                                        |                |                                                                                                                                                                    |                     |

| VSS           | GND                                          |                |                                                                                                                                                                    |                     |

| VSSP          | GND                                          |                |                                                                                                                                                                    |                     |

TABLE 4.3b lists various power-down states and conditions for each TMPR3922U pin. The "Power-Down Control" column shows the conditions which trigger a power-down for each respective pin. This column also shows the reset state for each of these conditions.

The "PON\* state" column defines the state of each pin at power-on reset (PON\*). This condition is defined as initial power up of the TMPR3922U, whereby the TMPR3922U is initialized and the TMPR3922U pins are reset to the state shown in the table. This state is entered after power is applied for the very first time (VSTANDBY is turned on but VCC3 is still turned off).

The "1st-time power-up state" column defines the state of each pin after power-up mode (RUNNING STATE) is executed for the first time. This mode is defined as VCC3 applied to the entire system and is initiated by the user pressing the ONBUTN while in the power-on reset (PON\*) state. Note that the defined state of various pins for 1st-time power-up may depend on the configuration of external devices attached to these pins. After 1st-time power-up, the software could change the state of various pins to be different from those shown in the table. Thereafter, subsequent transitions from SLEEP STATE to RUNNING STATE might result in different states for these pins.

The "power-down state" column defines the state of each pin during power-down mode (SLEEP STATE). This mode is defined as VCC3 turned off to the entire system, except for the TMPR3922U (RTC and interrupts alive) and any persistent memory.