# VR4101™

# **64-BIT MICROPROCESSOR**

## DESCRIPTION

NEC

The  $\mu$ PD30101 (VR4101) is one of NEC's VR series RISC (Reduced Instruction Set Computer) microprocessors and is a high-performance 64-bit microprocessor employing the MIPS RISC architecture.

The VR4101 is ideal for applications in battery-driven, high-performance portable information systems. This microprocessor uses the high-performance, super power-saving VR4100<sup>™</sup> as the CPU core, and has many peripheral circuits such as DMA, serial interface, keyboard interface, IrDA interface, touch panel interface, and real-time clock.

The functions of the VR4101 are explained in detail in the following manual. Be sure to refer to this manual when designing your system.

#### • VR4101 User's Manual (U12149E)

### **FEATURES**

- Employs 64-bit MIPS architecture

- · 5-stage pipeline

- Conforms to MIPS-III instruction set (Floating-point instructions are supported through software emulation.)

- Supports high-speed sum-of-products operation instructions

- Power consumption as low as 250 mW TYP. (at 33 MHz and 3.3 V)

- · Supports three types of power control modes

- External clock: 32 kHz, Internal operating frequency: 33 MHz

## **APPLICATIONS**

- · Battery-driven portable information systems

- Embedded controllers, etc.

## **ORDERING INFORMATION**

Part Number

Package

µPD30101GM-33-8ED

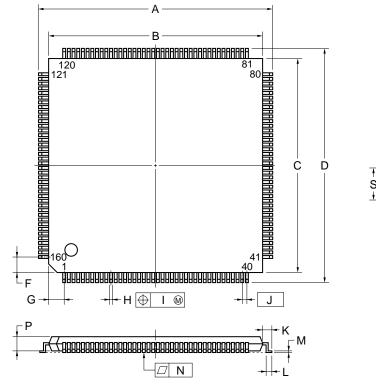

160-pin plastic LQFP (fine pitch) ( $24 \times 24$  mm)

The information in this document is subject to change without notice.

- Clock generator and PLL (× 1012)

- DRAM interface and ROM interface (Flash memory is also supported.)

- DMA controller (5 channels)

- Peripheral circuits ideal for portable systems LCD interface, keyboard interface, and touch panel interface

- IrDA controller

- Supports subset of ISA bus

- · Serial interface and debug serial interface

- Supply voltage: 3.0 to 3.6 V

- Package: 160-pin plastic LQFP

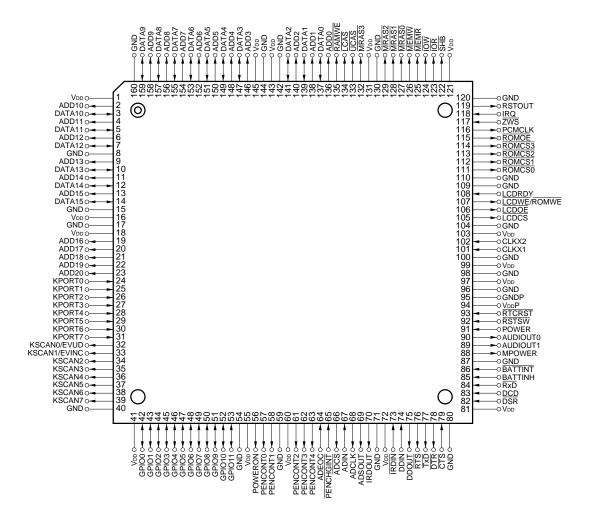

## **PIN CONFIGURATION**

# PIN NAME

| ADCLK         | : A/D Converter Clock         | LCAS          | : Lower Column Address Strobe |

|---------------|-------------------------------|---------------|-------------------------------|

| ADCS          | : A/D Converter Chip Select   | LCDCS         | : LCD Chip Select             |

| ADD (0:20)    | : Address Bus                 | LCDOE         | : LCD Output Enable           |

| ADEOC         | : A/D Converter End of Change | LCDRDY        | : LCD Ready                   |

| ADIN          | : A/D Converter Data In       | LCDWE         | : LCD Write Enable            |

| ADSOUT        | : A/D Converter Serial Out    | MEMR          | : Memory Read                 |

| AUDIOUT (0:1) | : Audio Out                   | MEMW          | : Memory Write                |

| BATTINH       | : Battery Inhibit             | MPOWER        | : Main Power On               |

| BATTINT       | : Battery Interrupt           | MRAS (0:3)    | : DRAM Row Address Strobe     |

| CLKX1         | : Clock X1                    | PCMCLK        | : PCM Clock                   |

| CLKX2         | : Clock X2                    | PENCHGINT     | : Pen Change Interrupt        |

| CTS           | : Clear to Send               | PENCONT (0:4) | : Touch Panel Control         |

| DATA (0:15)   | : Data Bus                    | POWER         | : Power On Switch             |

| DCD           | : Data Carrier Detection      | POWERON       | : Power On State              |

| DDIN          | : Debug Serial Data In        | RAMWE         | : DRAM Write Enable           |

| DDOUT         | : Debug Serial Data Out       | ROMCS (0:3)   | : ROM Chip Select             |

| DSR           | : Data Set Ready              | ROMOE         | : ROM Output Enable           |

| DTR           | : Data Terminal Ready         | ROMWE         | : ROM Write Enable            |

| EVINC         | : Electric Volume Input Clock | RSTOUT        | : PCM Reset                   |

| EVUD          | : Electric Volume Up/Down     | RSTSW         | : Reset Switch                |

| GND           | : Ground                      | RTCRST        | : Real Time Clock Reset       |

| GNDP          | : Quiet GND for PLL           | RTS           | : Request to Send             |

| GPIO (0:11)   | : General Purpose I/O         | RxD           | : Receive Data                |

| IOR           | : I/O Read                    | SHB           | : System Bus Hi-Byte Enable   |

| IOW           | : I/O Write                   | TxD           | : Transmit Data               |

| IRDIN         | : IrDA Data In                | UCAS          | : Upper Column Address Strobe |

| IRDOUT        | : IrDA Data Out               | Vdd           | : Power Supply Voltage        |

| IRQ           | : Interrupt Request           | VddP          | : Quiet VDD for PLL           |

| KPORT (0:7)   | : Key Scan Data In            | ZWS           | : Zero Wait State             |

| KSCAN (0:7)   | : Key Scan Data Out           |               |                               |

|               |                               |               |                               |

\_\_\_\_\_

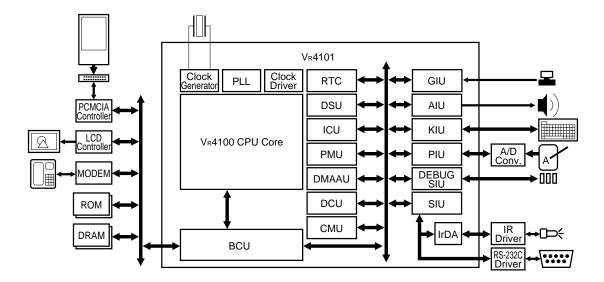

# INTERNAL BLOCK DIAGRAM AND EXAMPLE OF CONNECTION OF EXTERNAL BLOCKS

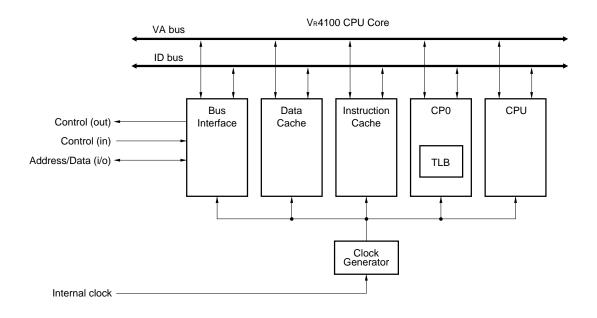

# **CPU CORE INTERNAL BLOCK DIAGRAM**

# TABLE OF CONTENTS

| 1. | PIN        | FUNCTIONS                                 | 8  |  |  |  |

|----|------------|-------------------------------------------|----|--|--|--|

|    | 1.1        | Pin Functions                             | 8  |  |  |  |

|    | 1.2        | Pin Status in Specific Status             | 12 |  |  |  |

| 2  | INTE       | RNAL BLOCKS                               | 14 |  |  |  |

| 2. | 2.1        | VR4100 CPU Core                           |    |  |  |  |

|    | 2.2        | BCU (Bus Control Unit)                    |    |  |  |  |

|    | 2.3        | RTC (Real-time Clock)                     |    |  |  |  |

|    | 2.4        | DSU (Deadman's Switch Unit)               |    |  |  |  |

|    | 2.5        | ICU (Interrupt Control Unit)              |    |  |  |  |

|    | 2.6        | PMU (Power Management Unit)               |    |  |  |  |

|    | 2.0        | DMAAU (Direct Memory Access Address Unit) |    |  |  |  |

|    | 2.8        | DCU (Direct Memory Access Control Unit)   |    |  |  |  |

|    | 2.9        | CMU (Clock Mask Unit)                     | -  |  |  |  |

|    |            | GIU (General Purpose I/O Unit)            |    |  |  |  |

|    |            | AlU (Audio Interface Unit)                |    |  |  |  |

|    |            | KIU (Keyboard Interface Unit)             | -  |  |  |  |

|    |            | PIU (Touch Panel Interface Unit)          |    |  |  |  |

|    |            | DebugSIU (Debug Serial Interface Unit)    |    |  |  |  |

|    |            | SIU (Serial Interface Unit)               |    |  |  |  |

|    | 2.15       |                                           | 15 |  |  |  |

| 3. | INTE       | RNAL ARCHITECTURE                         | 16 |  |  |  |

|    | 3.1        | Pipeline                                  |    |  |  |  |

|    | 3.2        | CPU Registers                             | 17 |  |  |  |

|    | 3.3        | Outline of Instruction Set                | 18 |  |  |  |

|    | 3.4        | System Control Coprocessor (CP0)          | 20 |  |  |  |

|    |            | 3.4.1 CP0 registers                       | 20 |  |  |  |

|    | 3.5        | Data Format and Addressing                | 22 |  |  |  |

|    | 3.6        | Virtual Storage                           | 23 |  |  |  |

|    |            | 3.6.1 Virtual address space               | 23 |  |  |  |

|    |            | 3.6.2 Address translation                 | 26 |  |  |  |

|    | 3.7        | Cache                                     | 28 |  |  |  |

|    | 3.8        | Exception Processing                      | 29 |  |  |  |

| 4. |            | ALIZATION INTERFACE                       | 32 |  |  |  |

| ч. | 4.1        | Reset Function                            |    |  |  |  |

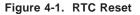

|    | 7.1        | 4.1.1 RTC reset                           |    |  |  |  |

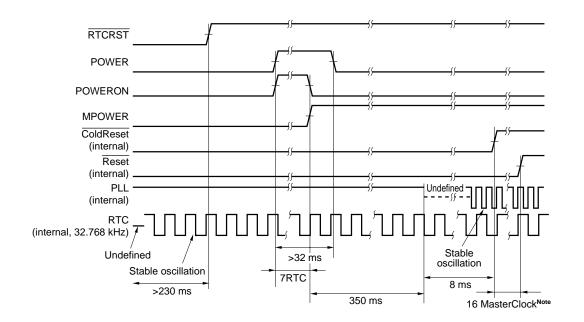

|    |            | 4.1.2 RSTSW                               |    |  |  |  |

|    |            | 4.1.3 Deadman's SW                        | -  |  |  |  |

|    |            | 4.1.4 Software shutdown                   |    |  |  |  |

|    |            | 4.1.5 HALTimer shutdown                   |    |  |  |  |

|    | 4.2        | CPU Core Registers at Reset               | -  |  |  |  |

|    | 4.2<br>4.3 | PowerOn Sequence                          |    |  |  |  |

|    | 4.3<br>4.4 | Modes of V <sub>R</sub> 4101              |    |  |  |  |

|    | 4.4        |                                           | 30 |  |  |  |

NEC

|     |                 | 4.4.1   | Power mode                           | 38 |  |

|-----|-----------------|---------|--------------------------------------|----|--|

|     |                 | 4.4.2   | Privilege mode                       | 39 |  |

|     |                 | 4.4.3   | Reverse endian                       | 39 |  |

|     |                 | 4.4.4   | Bootstrap exception vector (BEV)     | 39 |  |

|     |                 | 4.4.5   | Cache error check                    | 39 |  |

|     |                 | 4.4.6   | Inhibiting parity error              |    |  |

|     |                 | 4.4.7   | Enabling interrupts (IE)             |    |  |

|     |                 |         |                                      | 00 |  |

| 5   | BCI             |         | CONTROL UNIT)                        | 40 |  |

| 5.  | 5.1             |         |                                      |    |  |

|     | 5.1             | Genera  |                                      | 40 |  |

| c   |                 |         |                                      | 44 |  |

| 0.  |                 | •       | MA ADDRESS UNIT)                     |    |  |

|     | 6.1             | Genera  | 1                                    | 41 |  |

| _   |                 |         |                                      | 40 |  |

| 7.  |                 | •       | CONTROL UNIT)                        |    |  |

|     | 7.1             | Genera  | al                                   | 42 |  |

|     |                 |         |                                      |    |  |

| 8.  | СМ              | J (CLOO | CK MASK UNIT)                        | 43 |  |

|     | 8.1             | Genera  | 1                                    | 43 |  |

|     | 8.2             | Config  | uration                              | 43 |  |

|     |                 |         |                                      |    |  |

| 9.  | ICU             | (INTER  | RUPT CONTROL UNIT)                   | 44 |  |

|     | 9.1             | Genera  | al                                   | 44 |  |

|     | 9.2             |         | uration                              |    |  |

|     |                 | J J     |                                      |    |  |

| 10. | PML             | J (POW  | ER MANAGEMENT UNIT)                  | 46 |  |

|     |                 |         |                                      |    |  |

|     | 10.1            |         | Power mode                           |    |  |

|     |                 | 10.1.1  |                                      | 40 |  |

| 11  | PTC             |         | -TIME CLOCK UNIT)                    | 18 |  |

|     |                 | •       |                                      |    |  |

|     |                 |         |                                      |    |  |

|     | 11.2            | Config  | uration                              | 49 |  |

| 40  | DOU             |         |                                      | 50 |  |

| 12. |                 | •       | man's SW Unit)                       |    |  |

|     | 12.1            | Genera  | ıl                                   | 50 |  |

|     |                 |         |                                      | _  |  |

| 13. |                 | •       | RAL-PURPOSE I/O UNIT)                | 51 |  |

|     | 13.1            | Genera  | 11                                   | 51 |  |

|     |                 |         |                                      |    |  |

| 14. | PIU             | (TOUCI  | H PANEL INTERFACE UNIT)              | 52 |  |

|     | 14.1 General 52 |         |                                      |    |  |

|     | 14.2            | Examp   | le of External Circuit Configuration | 52 |  |

|     |                 |         |                                      |    |  |

| 15. | SIU             | (SERIA  | L INTERFACE UNIT)                    | 53 |  |

|     | 15.1 General    |         |                                      |    |  |

|     |                 |         | uration                              |    |  |

|     |                 | 5       |                                      |    |  |

| 16. AIU (AUDIO INTERFACE UNIT)             | 54 |  |  |  |

|--------------------------------------------|----|--|--|--|

| 16.1 General                               |    |  |  |  |

| 16.2 Configuration                         | 55 |  |  |  |

|                                            |    |  |  |  |

| 17. KIU (KEYBOARD INTERFACE UNIT)          |    |  |  |  |

| 17.1 General                               |    |  |  |  |

| 17.2 Configuration                         | 57 |  |  |  |

| 18. DebugSIU (DEBUG SERIAL INTERFACE UNIT) | E0 |  |  |  |

|                                            |    |  |  |  |

| 18.1 General                               | 58 |  |  |  |

| 19. INSTRUCTION SET                        | 59 |  |  |  |

| 19.1 Instruction Formats                   |    |  |  |  |

| 19.2 CPU Instruction Set List              |    |  |  |  |

| 19.3 Instruction Execution Time            | 64 |  |  |  |

| 20. ELECTRICAL SPECIFICATIONS              | 65 |  |  |  |

| 21. PACKAGE DRAWING                        | 92 |  |  |  |

| 22. RECOMMENDED SOLDERING CONDITIONS       |    |  |  |  |

# **1. PIN FUNCTIONS**

## 1.1 Pin Functions

# (1) System bus interface signals

| Signal Name | I/O    | Functional Description                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD (0:20)  | Output | 21-bit address bus. Used to specify addresses of DRAM, ROM, LCD, or PCMCIA.                                                                                                                                                                                                                                                                                                                   |

| DATA (0:15) | I/O    | 16-bit data bus. Used to transfer data from $V_{R}4101$ to DRAM, ROM, LCD, or PCMCIA, and vice versa.                                                                                                                                                                                                                                                                                         |

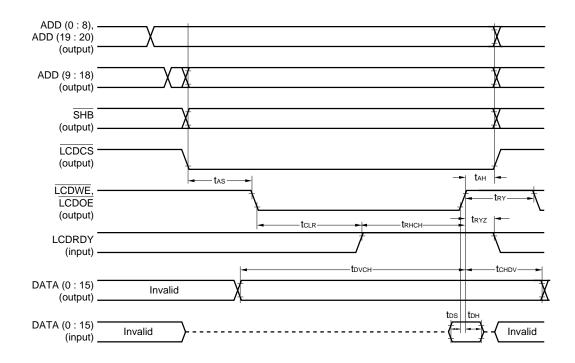

| LCDCS       | Output | LCD chip select signal. Asserted active when $V_{\mbox{\scriptsize R}}4101$ accesses LCD via ADD bus and DATA bus.                                                                                                                                                                                                                                                                            |

| LCDOE       | Output | LCD output enable signal. Asserted active when VR4101 reads data from LCD.                                                                                                                                                                                                                                                                                                                    |

| LCDWE/ROMWE | Output | Multiplexed signal of LCD write enable signal and flash memory write enable signal. This signal functions as LCD write enable signal when $\overline{LCDCS}$ pin is active, and is asserted active when VR4101 writes data to LCD. When $\overline{LCDCS}$ pin is inactive, this signal functions as ROM write enable signal, and is asserted active when VR4101 writes data to flash memory. |

| LCDRDY      | Input  | LCD ready signal. Assert this signal active when LCD or PCMCIA controller is ready for access by $V_R4101$ .                                                                                                                                                                                                                                                                                  |

| ROMCS (0:3) | Output | ROM chip select signals. Used to select ROM to be accessed from up to four ROMs connected to V_R4101.                                                                                                                                                                                                                                                                                         |

| ROMOE       | Output | ROM output enable signal. Asserted active when V <sub>R</sub> 4101 reads data from ROM.                                                                                                                                                                                                                                                                                                       |

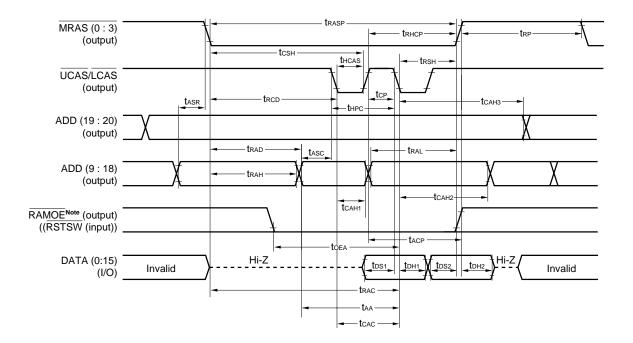

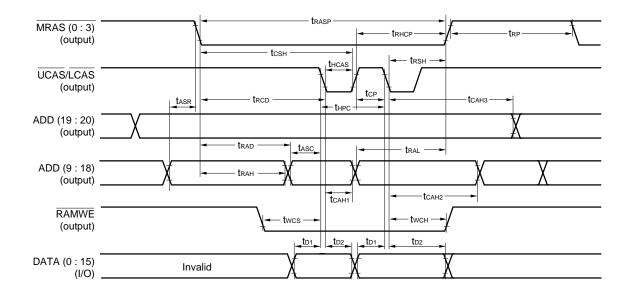

| MRAS (0:3)  | Output | RAS signals of DRAM. Asserted active when valid row address of RAM to be accessed is output onto ADD bus. Up to four RAMs can be connected to $V_R4101$ .                                                                                                                                                                                                                                     |

| UCAS        | Output | CAS signal of DRAM. Asserted active when valid column address is output onto ADD bus when high-order byte of DRAM is accessed.                                                                                                                                                                                                                                                                |

| LCAS        | Output | CAS signal of DRAM. Asserted active when valid column address is output onto ADD bus when low-order byte of DRAM is accessed.                                                                                                                                                                                                                                                                 |

| RAMWE       | Output | DRAM write enable signal. Asserted active when V <sub>R</sub> 4101 writes data to DRAM.                                                                                                                                                                                                                                                                                                       |

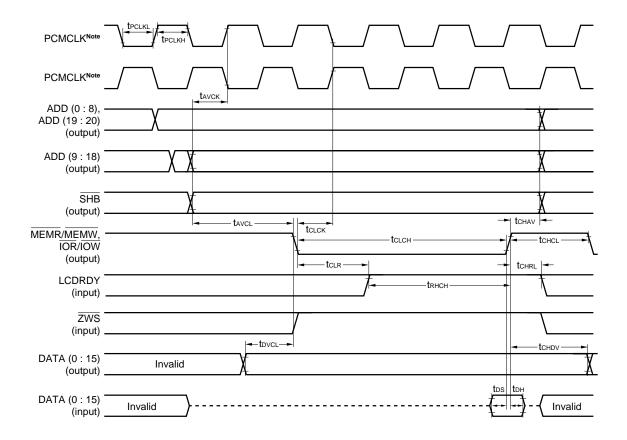

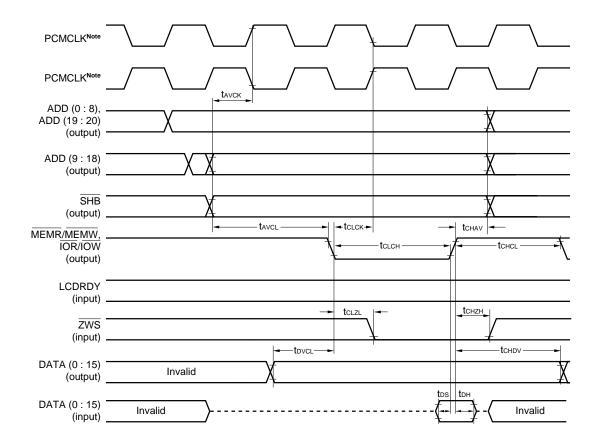

| PCMCLK      | Output | PCMCIA card clock. Outputs 8-MHz clock to be supplied to PCMCIA controller.                                                                                                                                                                                                                                                                                                                   |

| SHB         | Output | PCMCIA bus high byte enable signal. Asserted active if high-order byte of DATA bus is valid when PCMCIA is accessed.                                                                                                                                                                                                                                                                          |

| IOR         | Output | PCMCIA card I/O read signal. Asserted active when VR4101 reads data from I/O port of PCMCIA.                                                                                                                                                                                                                                                                                                  |

| ĪOW         | Output | PCMCIA card I/O write signal. Asserted active when VR4101 writes data to I/O of PCMCIA.                                                                                                                                                                                                                                                                                                       |

| MEMR        | Output | PCMCIA card memory read signal. Asserted active when $V_{\text{R}}4101$ reads data from memory of PCMCIA.                                                                                                                                                                                                                                                                                     |

| MEMW        | Output | PCMCIA card memory write signal. Asserted active when VR4101 writes data to memory of PCMCIA.                                                                                                                                                                                                                                                                                                 |

| ZWS         | Input  | PCMCIA zero wait state signal. Assert this signal active when PCMCIA controller is ready for access by $V_R4101$ .                                                                                                                                                                                                                                                                            |

| IRQ         | Input  | PCMCIA card interrupt request signal. PCMCIA controller asserts this pin active to                                                                                                                                                                                                                                                                                                            |

|             |        | inform V <sub>R</sub> 4101 of interrupt.                                                                                                                                                                                                                                                                                                                                                      |

# (2) Clock interface signals

| Signal Name | I/O   | Functional Description                                                           |

|-------------|-------|----------------------------------------------------------------------------------|

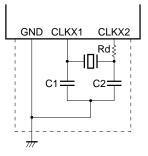

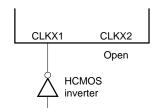

| CLKX1       | Input | 32-kHz clock input pin. Connect one end of 32-kHz crystal resonator to this pin. |

| CLKX2       | Input | 32-kHz clock input pin. Connect one end of 32-kHz crystal resonator to this pin. |

# (3) Battery monitor interface signals

| Signal Name | I/O   | Functional Description                                                                                                                                                                                                            |

|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

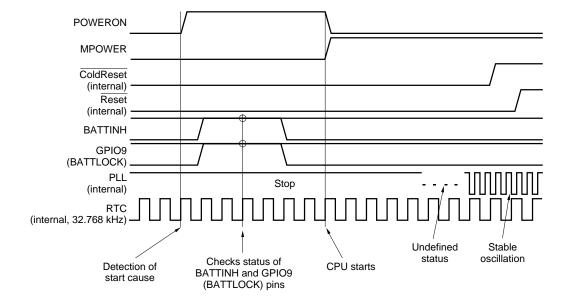

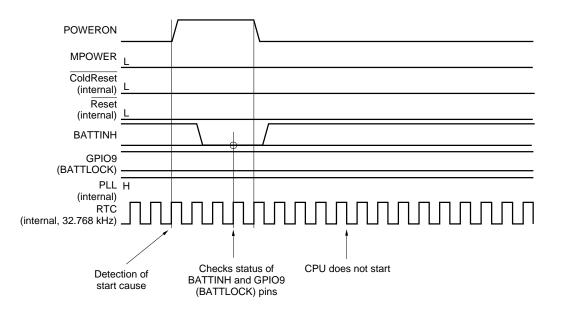

| BATTINH     | Input | Interrupt signal indicating battery voltage level on power application. External circuit checks battery voltage on power application and, if it judges that battery voltage is sufficient for operation, asserts this pin active. |

| BATTINT     | Input | Interrupt signal indicating battery voltage level during normal operation. External circuit checks battery voltage and, if it judges that battery voltage is not sufficient for operation, asserts this pin active.               |

# (4) Initialization interface signals

| Signal Name | I/O    | Functional Description                                                                                                                                                             |

|-------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MPOWER      | Output | Signal to turn ON main power. V $_{R}$ 4101 turns ON power supply to external DC/DC converter by asserting this pin active.                                                        |

| POWERON     | Output | Signal indicating that VR4101 is to start from Hibernate mode. It is asserted active when start cause is detected, and deasserted inactive after battery check has been completed. |

| POWER       | Input  | Signal indicating that power-ON switch has been pressed. When power-ON switch has been pressed, external circuit asserts this pin active.                                          |

| RSTSW       | Input  | Signal indicating that reset switch has been pressed. When reset switch has been pressed, external circuit asserts this pin active.                                                |

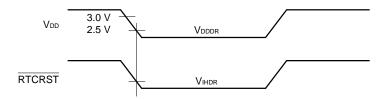

| RTCRST      | Input  | Signal resetting RTC. When power is supplied to system for first time, external circuit asserts this pin active for 230 ms.                                                        |

# (5) RS-232C interface signals

| Signal Name | I/O    | Functional Description                                                                                                                                                                                    |

|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxD         | Input  | Receive data signal. Used to transfer serial data from RS-232C driver/receiver to $V_{\text{R}}4101.$                                                                                                     |

| TxD         | Output | Transmit data signal. Used to transfer serial data from $V_{\text{R}}4101$ to RS-232C driver/receiver.                                                                                                    |

| RTS         | Output | Transmit request signal. VR4101 asserts this signal active when it wishes to transmit serial data.                                                                                                        |

| CTS         | Input  | Transmit enable signal. Assert this signal active when RS-232C driver/receiver is ready to receive serial data.                                                                                           |

| DCD         | Input  | Carrier detection signal. Assert this signal active while valid serial data is being received. If this signal is asserted active in Hibernate mode and in shutdown state, Fullspeed mode can be restored. |

| DTR         | Output | Terminal equipment ready signal. VR4101 asserts this signal active when it is ready to transmit/receive serial data.                                                                                      |

| DSR         | Input  | Data set ready signal. Assert this signal active when RS-232C driver/receiver and $V_R4101$ are ready to transmit/receive serial data.                                                                    |

# (6) IrDA interface signals

| Signal Name | I/O    | Functional Description                                                                                               |

|-------------|--------|----------------------------------------------------------------------------------------------------------------------|

| IRDIN       | Input  | IrDA serial data input signal. Used to transfer serial data from V $_{\rm R}4101$ to IrDA controller.                |

| IRDOUT      | Output | IrDA serial data output signal. Used to transfer serial data from IrDA controller to $V_{\mbox{\scriptsize R}}4101.$ |

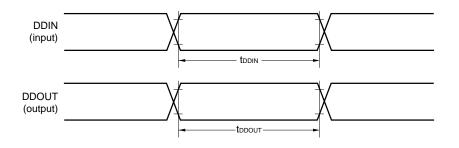

# (7) Debug serial interface signals

| Signal Name | I/O    | Functional Description                                                                                             |

|-------------|--------|--------------------------------------------------------------------------------------------------------------------|

| DDIN        | Input  | Debug serial data input signal. Used to transfer serial data from VR4101 to external debug serial controller.      |

| DDOUT       | Output | Debug serial data output signal. Used to transfer serial data from external debug serial controller to $V_R4101$ . |

# (8) Keyboard interface signals

| Signal Name  | I/O    | Functional Description                                                                                                                                                                                                                |

|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

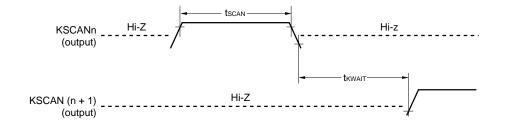

| KPORT (0:7)  | Input  | Keyboard scan data input signals. Used to scan input from keyboard.                                                                                                                                                                   |

| KSCAN (2:7)  | Output | Keyboard scan data output signals. Assert scan line active when input from keyboard is scanned.                                                                                                                                       |

| KSCAN1/EVINC | Output | Multiplexed signal of keyboard scan data output signal and electronic volume control clock signal. If EVINC pin is enabled to output by EVVOLREG register, this signal functions as clock output pin to electronic volume controller. |

| KSCAN0/EVUD  | Output | Multiplexed signal of keyboard scan data output signal and electronic volume Up/Down signal. When EVUD pin is enabled to output by EVVOLREG register, this signal functions as volume UP/DOWN pin for electronic volume controller.   |

# (9) Audio interface signals

| Signal Name    | I/O    | Functional Description                                                   |  |  |  |

|----------------|--------|--------------------------------------------------------------------------|--|--|--|

| AUDIOUT (0, 1) | Output | Audio output signals. Output audio signals when WAVE file is reproduced. |  |  |  |

## (10) Touch panel interface signals

| Signal Name   | I/O    | Functional Description                                                                                                          |  |  |  |

|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

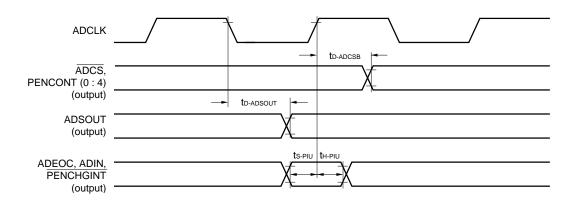

| ADCS          | Output | A/D converter chip select signal. This signal is asserted active when data is transferred or received to or from A/D converter. |  |  |  |

| ADCLK         | Output | Clock output signal to supply clock to A/D converter.                                                                           |  |  |  |

| ADIN          | Input  | Input pin to receive output data from A/D converter.                                                                            |  |  |  |

| ADSOUT        | Output | A/D converter serial data output signal. Used to output serial data to set A/D converter.                                       |  |  |  |

| ADEOC         | Input  | A/D converter data conversion end signal. Assert this signal active when A/D conversion by A/D conversion has been completed.   |  |  |  |

| PENCONT (0:4) | Output | Touch panel control signals. Output signals controlling voltage applied to touch panel.                                         |  |  |  |

| PENCHGINT     | Input  | Touch panel interrupt. External circuit asserts this pin active when touch panel is pressed.                                    |  |  |  |

# (11) General-purpose I/O signals

| Signal Name | I/O | Functional Description                                                                                    |

|-------------|-----|-----------------------------------------------------------------------------------------------------------|

| GPIO (0:11) | I/O | General-purpose I/O pins. However, fix function of GPIO9 to battery lid lock detection signal (BATTLOCK). |

# (12) Other signals

| Signal Name | I/O | Functional Description        |  |  |  |

|-------------|-----|-------------------------------|--|--|--|

| Vdd         |     | ositive power supply pin      |  |  |  |

| VddP        | _   | Power supply for internal PLL |  |  |  |

| GND         | —   | Ground pin                    |  |  |  |

| GNDP        | _   | Ground for internal PLL       |  |  |  |

# 1.2 Pin Status in Specific Status

| Pin Name    | At Reset by RTCRST | At Reset by Deadman's<br>SW or RSTSW | In Suspend Mode | In Hibernate Mode or<br>on shutdown by<br>HALTimer |

|-------------|--------------------|--------------------------------------|-----------------|----------------------------------------------------|

| ADD (0:20)  | 0                  | ×                                    | ×               | 0                                                  |

| DATA (0:15) | 0                  | ×                                    | ×               | 0                                                  |

| LCDCS       | Hi-Z               | 1                                    | 1               | Hi-Z                                               |

| LCDOE       | Hi-Z               | 1                                    | 1               | Hi-Z                                               |

| LCDWE/ROMWE | Hi-Z               | 1                                    | 1               | Hi-Z                                               |

| LCDRDY      | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| ROMCS (0:3) | Hi-Z               | 1                                    | 1               | Hi-Z                                               |

| ROMOE       | Hi-Z               | 1                                    | 1               | Hi-Z                                               |

| MRAS (0:3)  | 1                  | Hi-Z                                 | 0               | 0                                                  |

| UCAS        | 1                  | Hi-Z                                 | 0               | 0                                                  |

| LCAS        | 1                  | Hi-Z                                 | 0               | 0                                                  |

| RAMWE       | 1                  | 1                                    | 1               | 1                                                  |

| PCMCLK      | 0                  | ×                                    | ×               | 0                                                  |

| SHB         | 0                  | ×                                    | ×               | 0                                                  |

| IOR         | Hi-Z               | 1                                    | 1               | Hi-Z                                               |

| IOW         | Hi-Z               | 1                                    | 1               | Hi-Z                                               |

| MEMR        | Hi-Z               | 1                                    | 1               | Hi-Z                                               |

| MEMW        | Hi-Z               | 1                                    | 1               | Hi-Z                                               |

| ZWS         | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| IRQ         | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| RSTOUT      | Hi-Z               | 0                                    | Note            | Hi-Z                                               |

| CLKX1       | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| CLKX2       | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| BATTINH     | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| BATTINT     | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| MPOWER      | 0                  | 1                                    | 1               | 0                                                  |

| POWERON     | 0                  | 0                                    | 0               | 0                                                  |

| POWER       | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| RSTSW       | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| RTCRST      | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| RxD         | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| TxD         | 1                  | 1                                    | Note            | 1                                                  |

| RTS         | 1                  | 1                                    | Note            | 1                                                  |

| СТЅ         | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| DCD         | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| DTR         | 1                  | 1                                    | Note            | 1                                                  |

Note The status in the Fullspeed mode immediately before is retained.

Remark 0: Low-level output, 1: High-level output, Hi-Z: High impedance, x: Undefined

|               |                    |                                      |                 | (2/2)                                              |

|---------------|--------------------|--------------------------------------|-----------------|----------------------------------------------------|

| Pin Name      | At Reset by RTCRST | At Reset by Deadman's<br>SW or RSTSW | In Suspend Mode | In Hibernate Mode or<br>on shutdown by<br>HALTimer |

| DSR           | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| IRDIN         | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| IRDOUT        | Hi-Z               | Hi-Z                                 | Note            | Hi-Z                                               |

| DDIN          | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| DDOUT         | 1                  | 1                                    | Note            | 1                                                  |

| KPORT (0:7)   | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| KSCAN (2:7)   | Hi-Z               | Hi-Z                                 | Note            | Hi-Z                                               |

| KSCAN1/EVINC  | Hi-Z               | Hi-Z                                 | Note            | Hi-Z                                               |

| KSCAN0/EVUD   | Hi-Z               | Hi-Z                                 | Note            | Hi-Z                                               |

| AUDIOUT (0:1) | 0                  | 0                                    | 0               | 0                                                  |

| ADCS          | Hi-Z               | Hi-Z                                 | Note            | Hi-Z                                               |

| ADCLK         | 0                  | 0                                    | Note            | 0                                                  |

| ADIN          | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| ADSOUT        | 0                  | 0                                    | Note            | 0                                                  |

| ADEOC         | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| PENCONT (0:4) | Hi-Z               | Hi-Z                                 | Note            | Hi-Z                                               |

| PENCHGINT     | Hi-Z               | Hi-Z                                 | Hi-Z            | Hi-Z                                               |

| GPIO (0:11)   | Hi-Z               | Hi-Z                                 | Note            | Hi-Z                                               |

**Note** The status in the Fullspeed mode immediately before is retained.

Remark 0: Low-level output, 1: High-level output, Hi-Z: High impedance

# 2. INTERNAL BLOCKS

## 2.1 VR4100 CPU Core

## (1) CPU

The CPU processes integer instructions and consists of 64-bit register files, a 64-bit integer data bus, and a sum-of-products operation unit.

### (2) Coprocessor 0 (CP0)

The CP0 has a memory management unit (MMU) and an exception processing function. The MMU translates addresses and checks whether an access is made between different types (user, supervisor, or kernel) of memory segments. Virtual addresses are translated to physical addresses by TLB (high-speed translation lookaside buffer).

#### (3) Instruction cache

The instruction cache is of direct mapping, virtual index, and physical tag type.

#### (4) Data cache

The data cache is of direct mapping, virtual index, physical tag, and write back type.

## (5) CPU bus interface

The CPU bus interface controls data transfer between the VR4100 CPU core and BCU, one of the peripheral units. As the bus interface for the VR4100 CPU core, two 32-bit address/data multiplexed buses each for input and output, clock signals, and interrupt control signals are used.

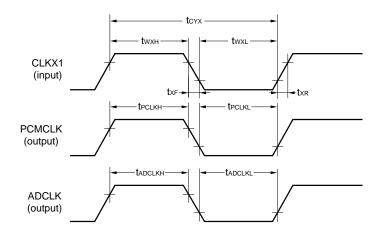

#### (6) Clock generator

A 32.768-kHz crystal oscillator is oscillated by an internal oscillation circuit and multiplied by 1012 by PLL (phase-locked loop) to generate a pipeline clock (PClock). The system interface clock (SClock) is generated from PClock.

## 2.2 BCU (Bus Control Unit)

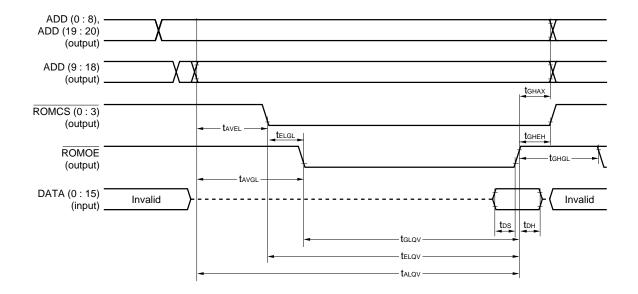

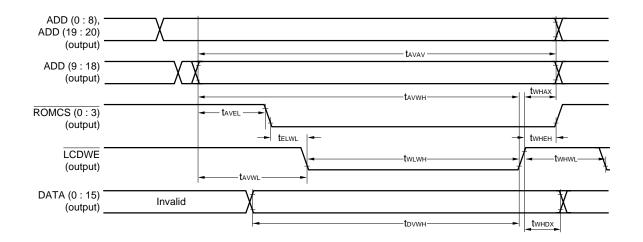

The BCU internally transfers data with the V<sub>R</sub>4100 CPU core via SysAD bus. It also controls the LCD controller, DRAM, ROM (flash memory or mask ROM), and PCMCIA controller connected to the system bus, and transfers data with the above devices via ADD and DATA buses.

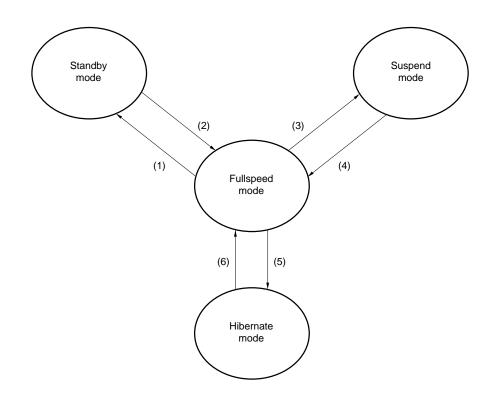

## 2.3 RTC (Real-time Clock)

The RTC has a precise counter that operates with a 32.768-kHz clock supplied from the clock generator. It also has several counters and compare registers for various interrupts.

### 2.4 DSU (Deadman's Switch Unit)

The DSU is used to check whether the processor is operating normally. If the software does not clear the register of this unit at specific intervals, the system is shut down.

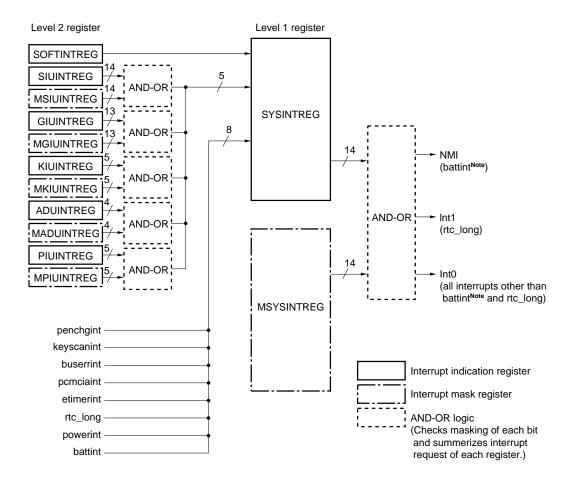

### 2.5 ICU (Interrupt Control Unit)

The ICU controls interrupt requests generated from the external and internal sources of the VR4101, and reports an interrupt request, if any, to the VR4100 CPU core.

## 2.6 PMU (Power Management Unit)

The PMU outputs signals necessary for controlling the power of the entire system, including the VR4101. It also controls the PLL of the VR4100 CPU core and the internal clocks (PClock, TClock, and MasterOut) in the power-saving mode.

## 2.7 DMAAU (Direct Memory Access Address Unit)

The DMAAU controls five types of DMA transfer addresses.

## 2.8 DCU (Direct Memory Access Control Unit)

The DCU controls arbitration of five types of DMA transfers.

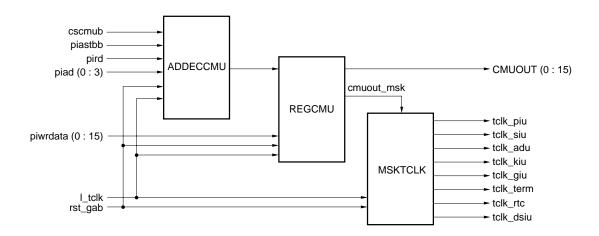

## 2.9 CMU (Clock Mask Unit)

The CMU controls supply of the clock (TClock or MasterOut) from the VR4100 CPU core to the internal peripheral units.

### 2.10 GIU (General Purpose I/O Unit)

The GIU controls 12 GPIO pins and the DCD pin. Note, however, that of the 12 GPIO pins, one is reserved for a specific application at present.

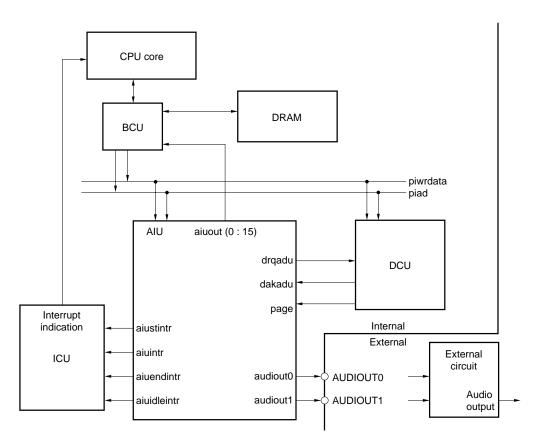

## 2.11 AIU (Audio Interface Unit)

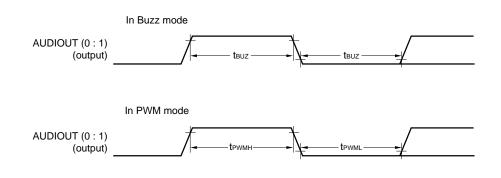

The AIU can be used to generate any frequency by using PWM and outputs audio signals to external devices. It also supplies a buzzer sound.

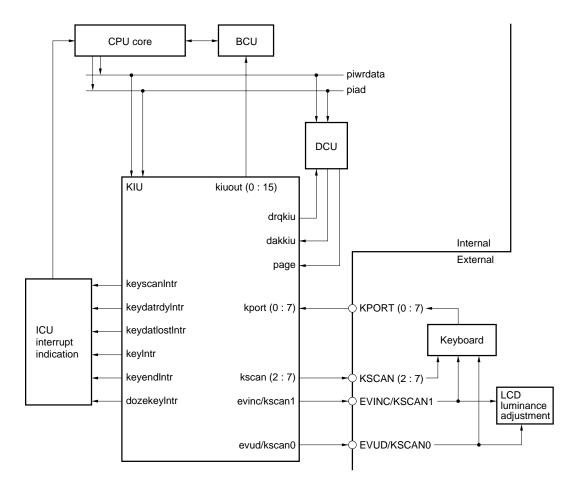

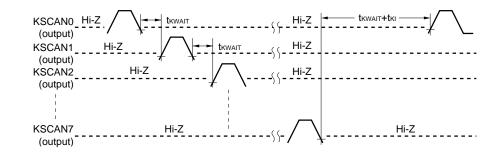

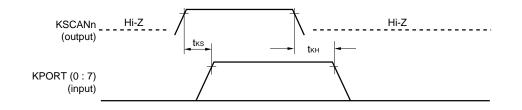

### 2.12 KIU (Keyboard Interface Unit)

The KIU has eight scan lines and eight detection lines to detect input of 64 keys. It can also detect roll over of 2 or 3 keys.

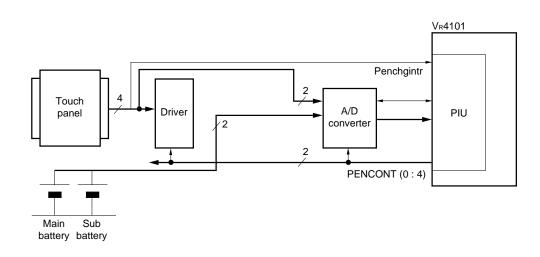

### 2.13 PIU (Touch Panel Interface Unit)

The PIU controls detection of touching on a touch panel. The VR4101 supports two types of A/D converter interfaces: TLC2543C and TLV1543C.

### 2.14 DebugSIU (Debug Serial Interface Unit)

The DebugSIU is a serial interface for debugging and supports a transfer rate of up to 115 kbps.

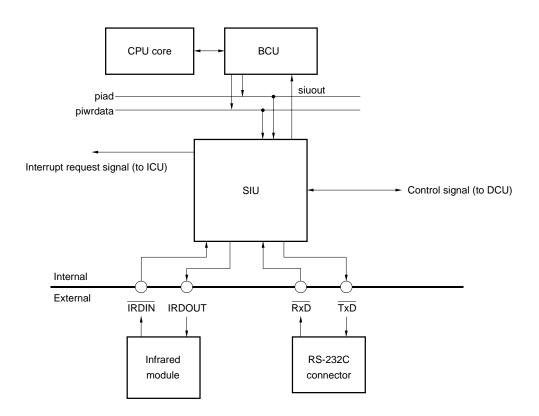

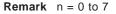

### 2.15 SIU (Serial Interface Unit)

The SIU is a serial interface conforming to the RS-232C Standards, and supports a transfer rate of up to 115 kbps. In addition, a IrDA serial interface that supports a transfer rate of 115 kbps is also included, though this IrDA serial interface is exclusively used with the RS-232C interface.

# 3. INTERNAL ARCHITECTURE

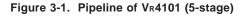

## 3.1 Pipeline

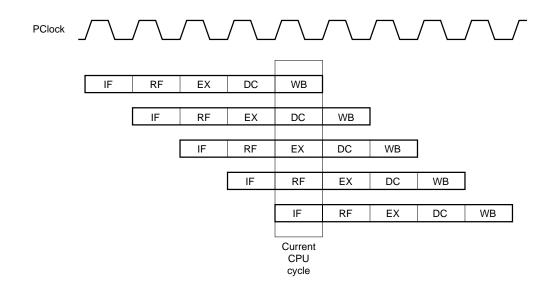

Each instruction is executed in the following five steps:

- (1) IF Instruction fetch

- (2) RF Register fetch

- (3) EX Execution

- (4) DC Data cache fetch

- (5) WB Write back

The VR4101 has a five-stage pipeline. It takes five clocks to execute each instruction, but instructions can be executed in parallel. The pipeline clock, PClock, operates at a frequency of 33 MHz.

The following figure outlines the pipeline.

## 3.2 CPU Registers

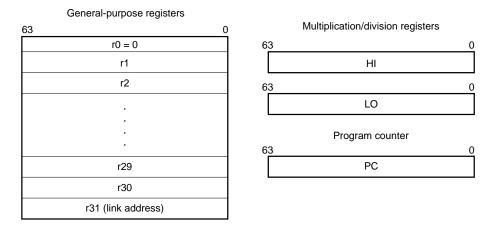

Figure 3-2 shows the CPU registers of the VR4101. The bit width of these registers is determined by the operation mode of the processor (32 bits in 32-bit mode or 64 bits in 64-bit mode).

Of the 32 general-purpose registers, the following two have a special meaning.

- Register r0 : The contents of this register are always 0. To discard the result of an operation, describe this register as the target of an instruction. When value 0 is necessary, this register can be used as a source register.

- Register r31 : This is a link register for the JAL and JALR instructions. Therefore, do not use this register with any other instructions.

The two multiplication/division registers (HI and LO) store the result of multiplication or sum-of-products operation, or quotient (LO) and remainder (HI) resulting from division.

Because the VR4101 does not support floating-point instructions, it is not provided with the 32 floating-point generalpurpose registers (FGR) found in the VR4200<sup>™</sup> and VR4400<sup>™</sup>.

**Remark** The load link bit (LL bit) used with synchronization instructions (LL and SC) for multi-processor system supported by the VR4200 and VR4400 is not provided in the VR4101 (refer to **3.3 (2) Deletion of multi-processor instructions**).

#### Figure 3-2. CPU Registers

The VR4101 does not have a program status word (PSW). The function of PSW is substituted by the status registers and cause registers incorporated to the system control coprocessor (CP0).

## 3.3 Outline of Instruction Set

Basically, the instruction set of the VR4101 conforms to the MIPS-I, -II, and -III instruction sets. However, it is different from those of the other processors in the VR series in the following four points. The difference between the VR4100 and VR4101 is that the VR4101 can manage operations including the peripheral functions by using power mode instructions (refer to (4)).

### (1) Deletion of floating-point (FPU) instructions

Because the VR4101 does not have a floating-point unit, it does not support FPU instructions. If an FPU instruction is encountered, therefore, a reserved instruction exception occurs. If it is necessary to use an FPU instruction, emulate the instruction in software in an exception handler.

#### (2) Deletion of multi-processor instructions

The VR4101 does not support a multiple processor operating environment. If a synchronization support instruction (LL or SC instruction) defined by MIPS-II and -III ISA is encountered, a reserved instruction exception occurs. In addition, the load link bit (LL bit) is also unavailable.

The VR4101 executes all load/store instructions in the programmed sequence. Therefore, the SYNC instruction is treated as a NOP instruction.

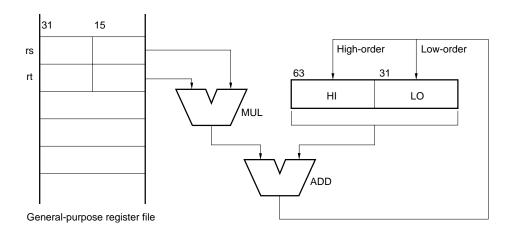

#### (3) Addition of sum-of-products instructions

The VR4101 has a dedicated sum-of-products operation core in the CPU and additional integer sum-ofproducts operation instructions, in order to execute sum-of-products operation at high speeds. Note that these instructions are not correctly executed with any other processors in the V<sub>R</sub> series. The operations by the sum-of-products instructions are as follows:

#### (a) MADD16 (Multiply and Add 16-bit Integer)

This instruction multiplies the contents of general-purpose register rs by the contents of general-purpose register rt. Both the operands are treated as signed 16-bit integers. Bits 62 through 15 of both the operands must be sign-extended.

The result of the multiplication is added to a 64-bit value combining special registers HI and LO. The low-order word (64 bits) of the result is loaded to special register LO, and the high-order word is loaded to HI.

An integer overflow exception does not occur.

Figure 3-3 outline the operation of the MADD16 instruction.

#### Figure 3-3. Operation of MADD16 Instruction

#### (b) DMADD16 (Doubleword Multiply and Add 16-bit register)

This instruction multiplies the contents of general-purpose register rs by the contents of general-purpose register rt. Both the operands are treated as signed 16-bit integers. Bits 62 through 15 of both the operands must be sign-extended.

The result of the multiplication is added to the value of special register LO. The result of the addition is treated as a signed integer. The 64-bit result is loaded to special register LO.

An integer overflow exception does not occur.

This operation is defined in the 64-bit mode and 32-bit kernel mode. If this instruction is encountered in the 32-bit user/supervisor mode, a reserved instruction exception occurs.

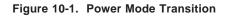

#### (4) Addition of power mode instructions

The VR4101 supports three power modes to lower the power consumption, and therefore, has dedicated instructions that set these modes. Note that the power mode instructions are not correctly executed by any other processors in the VR series.

The operations of the power mode instructions are as follows:

#### (a) STANDBY

This instruction places the processor in the Standby mode from the Fullspeed mode.

When instruction execution has proceeded to the WB stage, and the SysAD bus has entered the idle status, the internal clock is fixed to the high level, and the pipeline operation is stopped.

In the Standby mode, the PLL, clocks related to timers/interrupts, and interface clocks to the peripheral function blocks (TClock and MasterOut) operate normally.

When the processor is in the Standby mode it is returned to the Fullspeed mode by any interrupt including an internally generated timer interrupt.

## (b) SUSPEND

This instruction places the processor in the Suspend mode from the Fullspeed mode.

When instruction execution has proceeded to the WB stage, and the SysAD bus has entered the idle status, the internal clock and TClock are fixed to the high level, and the pipeline operation and interfacing to the peripheral function blocks are stopped.

In the Suspend mode, the PLL, clocks related to timers/interrupts, and MasterOut operate normally. The processor remains in the Suspend mode until it accepts an interrupt. When the processor accepts an interrupt, it returns to the Fullspeed mode.

## (c) HIBERNATE

This instruction places the processor in the Hibernate mode from the Fullspeed mode.

When instruction execution has proceeded to the WB stage, and the SysAD bus has entered the idle status, all the clocks are fixed to the high level, and the pipeline operation is stopped.

The processor remains in the Hibernate mode until either the POWER pin is asserted active or the WakeUp timer interrupt occurs. The processor returns to the Fullspeed mode when the POWER pin is asserted active, when the WakeUp Timer interrupt occurs, or when the DCD pin is asserted active.

## 3.4 System Control Coprocessor (CP0)

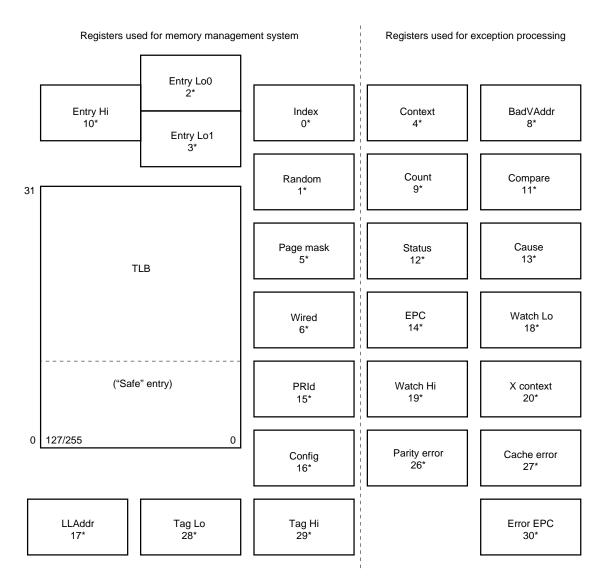

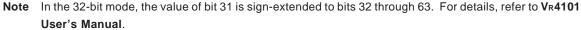

CP0 supports memory management, address translation, exception processing, and privilege operations. CP0 has the registers shown in Table 3-1, and a 32-entry TLB.

The basic configuration of the CP0 registers of the VR4101 is the same as that of the VR4200 and VR4400. However, because the number of entries of TLB, page size, cache size, physical address space, and system interface differ between the VR4101 and VR4200/VR4400, the bit configuration and setting differ. For details, refer to **VR4101 User's Manual**.

#### 3.4.1 CP0 registers

All the CP0 registers that can be used with the VR4101 are listed below. Writing to or reading from an unused register (RFU) is undefined. In the 32-bit mode, the high-order 32 bits of 64-bit registers are masked.

Remark "\*" indicates a register number.

| Table 3-    | 1. CP0 | Registers  |

|-------------|--------|------------|

| 1 4 5 1 0 0 |        | 1109101010 |

| No.   | Register     | Description                                           |

|-------|--------------|-------------------------------------------------------|

| 0     | Index        | Programmable pointer to TLB array                     |

| 1     | Random       | Dummy random pointer to TLB array (read-only)         |

| 2     | Entry Lo0    | Latter half of TLB entry for even-number VPN          |

| 3     | Entry Lo1    | Latter half of TLB entry for odd-number VPN           |

| 4     | Context      | Pointer to virtual PTE table of kernel in 32-bit mode |

| 5     | Page mask    | Specifies page size                                   |

| 6     | Wired        | Number of wired TLB entries                           |

| 7     | —            | RFU (Reserved for Future Use)                         |

| 8     | BadVAddr     | Indicates virtual address at which error occurs last  |

| 9     | Count        | Timer count                                           |

| 10    | Entry Hi     | First half of TLB entry (including ASID)              |

| 11    | Compare      | Timer compare value                                   |

| 12    | Status       | Sets operation status                                 |

| 13    | Cause        | Indicates cause of last exception                     |

| 14    | EPC          | Exception program counter                             |

| 15    | PRId         | Processor revision ID                                 |

| 16    | Config       | Sets memory system mode                               |

| 17    | LLAddr       | RFU                                                   |

| 18    | Watch Lo     | Low-order bits of memory reference trap address       |

| 19    | Watch Hi     | High-order bits of memory reference trap address      |

| 20    | X context    | Pointer to virtual PTE table of kernel in 64-bit mode |

| 21-25 | _            | RFU                                                   |

| 26    | Parity error | Parity bit of cache                                   |

| 27    | Cache error  | Error and status register of cache                    |

| 28    | Tag Lo       | Cache tag register, low                               |

| 29    | Tag Hi       | Cache tag register, high (reserved register)          |

| 30    | Error EPC    | Error exception program counter                       |

| 31    | _            | RFU                                                   |

NEC

## 3.5 Data Format and Addressing

The V $_{R}$ 4101 uses the following four data formats:

- Double word (64 bits)

- Word (32 bits)

- Half word (16 bits)

- Byte (8 bits)

The byte ordering is set by the BE bit of the config register. With the current VR4101, set little endian.

| 3                     | 1 24 | 23 16 | 15 8 | 7 0 | Word<br>address |

|-----------------------|------|-------|------|-----|-----------------|

| High-order<br>address | 15   | 14    | 13   | 12  | 12              |

| t                     | 11   | 10    | 9    | 8   | 8               |

|                       | 7    | 6     | 5    | 4   | 4               |

| Low-order<br>address  | 3    | 2     | 1    | 0   | 0               |

Figure 3-5. Byte Address in Word: Little Endian

Remarks 1. The least significant byte is the lowest address.

2. A word is addressed by the address of the least significant byte.

|                       | Word |    |    |            | Half | word |      | Byte |             |

|-----------------------|------|----|----|------------|------|------|------|------|-------------|

| (                     | 63   |    |    | 32 31 16 1 |      |      | 15 8 | 7 (  | Double word |

| High-order<br>address | 23   | 22 | 21 | 20         | 19   | 18   | 17   | 16   | 16          |

|                       | 15   | 14 | 13 | 12         | 11   | 10   | 9    | 8    | 8           |

| Low-order<br>address  | 7    | 6  | 5  | 4          | 3    | 2    | 1    | 0    | 0           |

#### Figure 3-6. Byte Address in Double Word: Little Endian

Remarks 1. The least significant byte is the lowest address.

2. A word is addressed by the address of the least significant byte.

# 3.6 Virtual Storage

The VR4101 has a virtual storage management mechanism using TLB.

Virtual addresses are used for address management by software or address calculation of the pipeline. To access memories for program fetch and data access, and internal I/O and external I/O, physical addresses translated by TLB are used.

Note that part of the virtual address space is not translated by TLB, but is translated to physical addresses by merely changing specific addresses. If only this part of the address space is used, the VR4101 can be treated in the same manner as a CPU that operates with physical addresses.

#### 3.6.1 Virtual address space

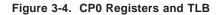

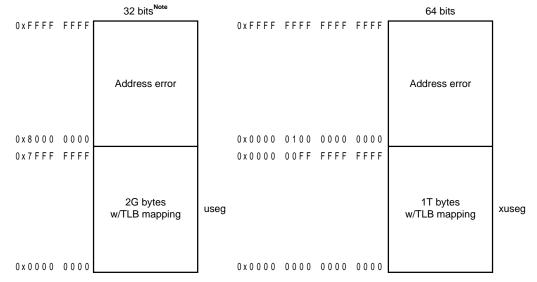

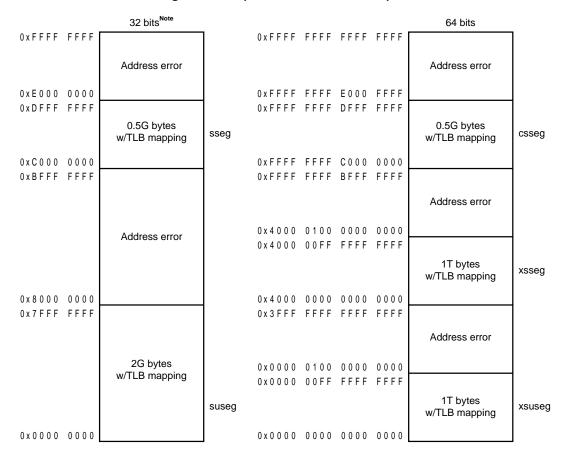

The VR4101 has two operation modes, 32-bit mode and 64-bit mode, and three types of operating modes: user mode, supervisor mode, and kernel mode. The virtual address space in each mode is shown below.

#### Figure 3-7. User Mode Address Space

#### Figure 3-8. Supervisor Mode Address Space

Note In the 32-bit mode, the value of bit 31 is sign-extended to bits 32 through 63. For details, refer to VR4101 User's Manual.

|                            | 32 bits <sup>Note 1</sup>                      |       |                            |              |                    |                    | 64 bits                                                           |        |

|----------------------------|------------------------------------------------|-------|----------------------------|--------------|--------------------|--------------------|-------------------------------------------------------------------|--------|

| 0xFFFF FFFF                | 0.5G bytes                                     |       | 0 x F F F F<br>0 x F F F F |              |                    | F F F F<br>0 0 0 0 | 0.5G bytes<br>w/TLB mapping                                       | ckseg3 |

| 0xF000 0000                | w/TLB mapping                                  | kseg3 | 0 x F F F F<br>0 x F F F F | FFFF         | DFFF               |                    | 0.5G bytes<br>w/TLB mapping                                       | cksseg |

| 0xDFFF FFFF                | 0.5G bytes                                     | -     | 0 x F F F F                | FFFF         | BFFF               | FFFF               | 0.5G bytes<br>w/o TLB mapping<br>Uncacheable                      | ckseg1 |

|                            | w/TLB mapping                                  | ksseg | 0 x F F F F<br>0 x F F F F | FFFF         | 9 F F F            | FFFF               | 0.5G bytes<br>w/o TLB mapping<br>Cacheable <sup>№ote 2</sup>      | ckseg0 |

| 0xC000 0000<br>0xBFFF FFFF |                                                | -     | 0 x F F F F<br>0 x F F F F |              | 8 0 0 0<br>7 F F F |                    |                                                                   |        |

|                            | 0.5G bytes                                     |       | 0 x C 0 0 0                | 0 0 F F      | 8000               | 0000               | Address error                                                     |        |

|                            | w/o TLB mapping<br>Uncacheable                 | kseg1 | 0 x C 0 0 0                | 0 0 F F      | 7 F F F            | FFFF               | w/TLB mapping                                                     | xkseg  |

| 0xA000 0000<br>0x9FFF FFFF |                                                | -     | 0 x C 0 0 0<br>0 x B F F F | 0000<br>FFFF | 0000<br>FFFF       | 0000<br>FFFF       |                                                                   | -      |

| 0,3111 1111                | 0.5G bytes                                     |       | 0x8000                     |              |                    |                    | No TLB mapping<br>(For details, refer<br>to <b>Figure 3-10.</b> ) | xkphys |

|                            | w/o TLB mapping<br>Cacheable <sup>Note 2</sup> | kseg0 | 0 x 7 F F F                | FFFF         | FFFF               | FFFF               | Address error                                                     |        |

| 0x8000 0000<br>0x7FFF FFFF |                                                | -     | 0 x 4 0 0 0<br>0 x 4 0 0 0 |              |                    |                    |                                                                   | -      |

| UX/FFF FFFF                |                                                |       | 0 x 4 0 0 0                |              | 0000               |                    | 1T bytes<br>w/TLB mapping                                         | xksseg |

|                            | 2G bytes<br>w/TLB mapping                      | kuseg | 0 x 3 F F F                | FFFF         |                    | FFFF               | Address error                                                     |        |

|                            |                                                |       | 0 x 0 0 0 0<br>0 x 0 0 0 0 | 0100         | 0000               | 0000               |                                                                   | 4      |

|                            |                                                |       |                            |              |                    |                    | 1T bytes<br>w/TLB mapping                                         | xkuseg |

| 0x0000 0000                |                                                | J     | 0 x 0 0 0 0                | 0000         | 0000               | 0000               |                                                                   | J      |

Figure 3-9. Kernel Mode Address Space

- Notes 1. In the 32-bit mode, the value of bit 31 is sign-extended to bits 32 through 63. For details, refer to VR4101 User's Manual.

- 2. Whether this area is used as a cache area is specified by the K0 field of the config register.

| 0xBFFF FFFF FFFF FFF                         | F Address error                |

|----------------------------------------------|--------------------------------|

| 0xB800 0001 0000 000                         |                                |

| 0xB800 0000 FFFF FFF                         | 40 Dytes                       |

| 0xB800 0000 0000 000                         | w/o TLB mapping                |

| 0xB800 0000 0000 000<br>0xB7FF FFFF FFFF FFF |                                |

|                                              | Address error                  |

| 0xB000 0001 0000 000                         |                                |

| 0xB000 0000 FFFF FFF                         | 4G bytes<br>w/o TLB mapping    |

| 0xB000 0000 0000 000                         |                                |

| 0xAFFF FFFF FFFF FFF                         | F                              |

|                                              | Address error                  |

| 0xA800 0001 0000 000<br>0xA800 0000 FFFF FFF |                                |

|                                              | F 4G bytes<br>w/o TLB mapping  |

| 0xA800 0000 0000 000                         | an ah a ah la                  |

| 0xA7FF FFFF FFFF FFF                         |                                |

| 0xA000 0001 0000 000                         | Address error                  |

| 0xA000 0000 FFFF FFF                         |                                |

|                                              | w/o TLB mapping                |

| 0xA000 0000 0000 000                         |                                |

| 0x9FFF FFFF FFFF FFF                         |                                |

| 0x9800 0001 0000 000                         | Address error                  |

| 0x9800 0000 FFFF FFF                         | F 4G bytes                     |

|                                              | w/o TLB mapping                |

| 0x9800 0000 0000 000<br>0x97FF FFFF FFFF FFF |                                |

|                                              | Address error                  |

| 0x9000 0001 0000 000                         |                                |

| 0x9000 0000 FFFF FFF                         | 40 Dytes                       |

| 0x9000 0000 0000 000                         | w/o TLB mapping                |

| 0x8FFF FFFF FFFF FFF                         | -                              |

|                                              | Address error                  |

| 0x8800 0001 0000 000                         |                                |

| 0x8800 0000 FFFF FFF                         | 40 Dytes                       |

| 0x8800 0000 0000 000                         | w/o TLB mapping<br>Uncacheable |

| 0x87FF FFFF FFFF FFF                         |                                |

|                                              | Address error                  |

| 0x8000 0001 0000 000<br>0x8000 0000 FFFF FFF |                                |

| 0X0000 0000 FFFF FFF                         | 4G bytes<br>w/o TLB mapping    |

| 0x8000 0000 0000 000                         | Lincacheable                   |

|                                              |                                |

#### Figure 3-10. Details of xkphys Area

#### 3.6.2 Address translation

Virtual addresses are translated into physical addresses by the internal TLB (Translation Lookaside Buffer) in page units. The TLB has a full-associative configuration and has 64 entries at the virtual address side and 32 entries at the physical address side. The page size is variable from 1K to 256K byte.

If a TLB entry is not found, a TLB non-coincidence exception occurs in the 32-bit mode, and an XTLB non-coincidence exception occurs in the 64-bit mode. Change the contents of the TLB in software.

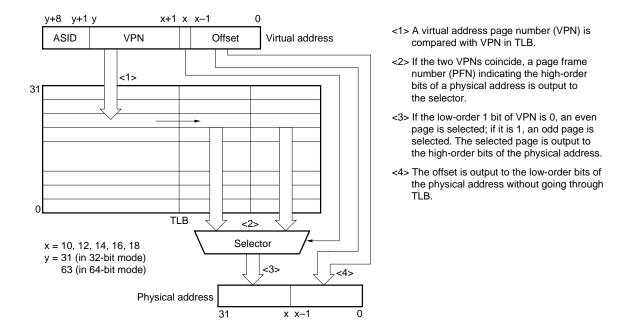

The following figure outlines address translation.

#### Figure 3-11. Outline of Address Translation

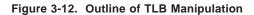

The TLB entry is read or written by loading/storing among the TLB entry indicated by the index register and random register, entry Hi, entry Lo1, entry Lo0, and page mask registers. How the TLB is manipulated is illustrated below.

# NEC

# 3.7 Cache

# (1) Instruction cache

The instruction cache has the following features:

- Internal cache memory

- Capacity: 2K bytes

- Direct mapping mode

- Virtual index address

- Physical tag check

- 4-word (16-byte) cache line

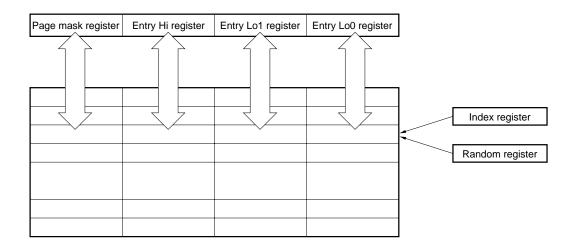

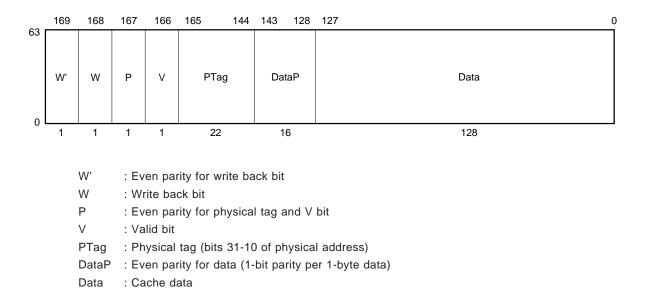

## Figure 3-13. Format of Instruction Cache

- Data : Cache data

- P : Even parity for physical tag and V bit

- DataP : Even parity for data (1-bit parity per 4-byte data)

## (2) Data cache

The data cache has the following features:

- Internal cache memory

- Capacity: 1K bytes

- Write back

- Direct mapping mode

- Virtual index address

- Physical tag check

- 4-word (16-byte) cache line

#### Figure 3-14. Format of Data Cache

## 3.8 Exception Processing

The VR4101 enters the kernel mode in which interrupts are disabled when an exception occurs, and executes an exception handler from a fixed exception vector address. To restore from the exception, the program counter, operating mode, and interrupt enable information must be restored to the original status. Save this information when the interrupt occurs.

When an interrupt occurs, the EPC register holds the address of the instruction that has caused the exception, or the address of the instruction immediately before if the exception has occurred in the branch delay slot. This means that the EPC register stores the address from which execution is to be started after the exception has been processed. At reset and on occurrence of NMI, the EPC register holds a restart address.

| Exception                                  | Symbol    | Description                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

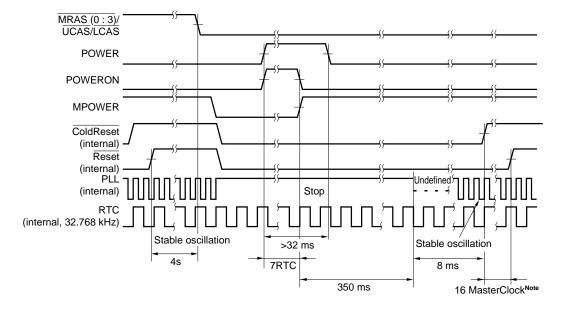

| Cold reset                                 |           | This exception occurs if the ColdReset (internal) and Reset (internal) signals are simultaneously asserted active (for details, refer to <b>Figures 4-1</b> through <b>4-5</b> ). As a result, the instruction execution is stopped, and the handler on the reset vector is executed. The internal status, except some bits of the status registers, is undefined. |

| Soft reset                                 | _         | This exception occurs if the Reset (internal) signal is asserted active. As a result, the instruction execution is stopped, and the handler on the reset vector is executed. The internal status before soft reset is retained. However, the current $V_R4101$ does not support soft reset.                                                                        |

| NIMI                                       | —         | This exception occurs if the NMI (internal) signal is asserted active.                                                                                                                                                                                                                                                                                             |

| TLB non-coincidence                        | TLBL/TLBS | This exception occurs if there is no TLB entry that coincides with an address to be referenced in the 32-bit mode.                                                                                                                                                                                                                                                 |

| Extended addressing<br>TLB non-coincidence | TLBL/TLBS | This exception occurs if there is no TLB entry that coincides with an address to be referenced in the 64-bit mode.                                                                                                                                                                                                                                                 |

| TLB invalid                                | TLBL/TLBS | This exception occurs if the TLB entry that coincides with the virtual address to be referenced is invalid (V bit = 0).                                                                                                                                                                                                                                            |

| TLB modify                                 | Mod       | This exception occurs if the TLB entry that coincides with the virtual address to be referenced is valid but is disabled from being written (D bit = 0) when the store instruction is executed.                                                                                                                                                                    |

| Bus error                                  | IBE/DBE   | This exception occurs when the external agent indicates an error of data on the SysCmd bus by using an external interrupt to the bus interface (bus time-out, bus parity error, or invalid physical memory address or access type).                                                                                                                                |

| Address error                              | AdEL/AdES | This exception occurs if an attempt is made to execute the LH, SH/LW/SW, LD, or SD instruction to the half word/word/double word not located at the half word/ word/double word boundary, or if an attempt is made to reference the virtual address that cannot be accessed.                                                                                       |

| Integer overflow                           | Ov        | This exception occurs if a 2's complement overflow occurs as a result of addition or subtraction.                                                                                                                                                                                                                                                                  |

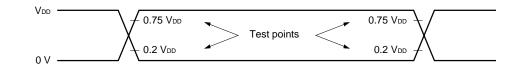

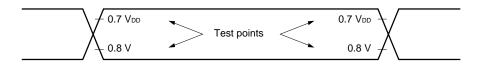

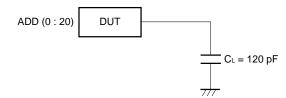

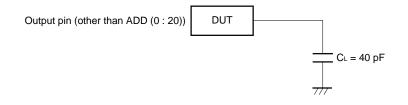

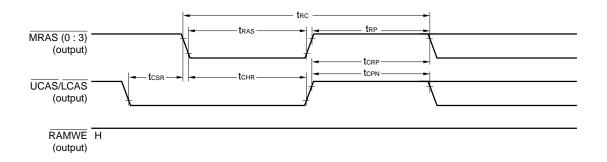

| Trap                                       | Tr        | This exception occurs if the condition is true as a result of executing the trap instruction.                                                                                                                                                                                                                                                                      |